### **D1-USER-M User Manual**

Manual Number: D1-USER-M

**NOTE:** Modules F1-130-DD, F1-130-DD-D, F1-130AA, F1-130DA, F1-130DR-D, F1-130DR, F1-10CON, and F1-130AR have been discontinued. Terminal blocks B-F1130DR and B-F1130AR are also discontinued. Please consider Productivity, CLICK, or BRX systems as a replacement platform.

### ~ WARNING ~

Thank you for purchasing automation equipment from AutomationDirect.com®, doing business as, AutomationDirect. We want your new automation equipment to operate safely. Anyone who installs or uses this equipment should read this publication (and any other relevant publications) before installing or operating the equipment.

To minimize the risk of potential safety problems, you should follow all applicable local and national codes that regulate the installation and operation of your equipment. These codes vary from area to area and usually change with time. It is your responsibility to determine which codes should be followed, and to verify that the equipment, installation, and operation is in compliance with the latest revision of these codes.

At a minimum, you should follow all applicable sections of the National Fire Code, National Electrical Code, and the codes of the National Electrical Manufacturer's Association (NEMA). There may be local regulatory or government offices that can also help determine which codes and standards are necessary for safe installation and operation.

Equipment damage or serious injury to personnel can result from the failure to follow all applicable codes and standards. We do not guarantee the products described in this publication are suitable for your particular application, nor do we assume any responsibility for your product design, installation, or operation.

Our products are not fault-tolerant and are not designed, manufactured or intended for use or resale as on-line control equipment in hazardous environments requiring fail-safe performance, such as in the operation of nuclear facilities, aircraft navigation or communication systems, air traffic control, direct life support machines, or weapons systems, in which the failure of the product could lead directly to death, personal injury, or severe physical or environmental damage ("High Risk Activities"). AutomationDirect specifically disclaims any expressed or implied warranty of fitness for High Risk Activities.

For additional warranty and safety information, see the Terms and Conditions section of our catalog. If you have any questions concerning the installation or operation of this equipment, or if you need additional information, please call us at 770-844-4200.

This publication is based on information that was available at the time it was printed. At **AutomationDirect** we constantly strive to improve our products and services, so we reserve the right to make changes to the products and/or publications at any time without notice and without any obligation. This publication may also discuss features that may not be available in certain revisions of the product.

### **Trademarks**

This publication may contain references to products produced and/or offered by other companies. The product and company names may be trademarked and are the sole property of their respective owners. **AutomationDirect** disclaims any proprietary interest in the marks and names of others.

### Copyright 2021, AutomationDirect.com Incorporated All Rights Reserved

No part of this manual shall be copied, reproduced, or transmitted in any way without the prior, written consent of **AutomationDirect.com Incorporated**. **AutomationDirect** retains the exclusive rights to all information included in this document.

# ADVERTENCIA /

Gracias por comprar equipo de automatización de Automationdirect.com<sup>®</sup>. Deseamos que su nuevo equipo de automatización opere de manera segura. Cualquier persona que instale o use este equipo debe leer esta publicación (y cualquier otra publicación pertinente) antes de instalar u operar el equipo.

Para reducir al mínimo el riesgo debido a problemas de seguridad, debe seguir todos los códigos de seguridad locales o nacionales aplicables que regulan la instalación y operación de su equipo. Estos códigos varian de área en área y usualmente cambian con el tiempo. Es su responsabilidad determinar cuales códigos deben ser seguidos y verificar que el equipo, instalación y operación estén en cumplimiento con la revisión mas reciente de estos códigos.

Como mínimo, debe seguir las secciones aplicables del Código Nacional de Incendio, Código Nacional Eléctrico, y los códigos de (NEMA) la Asociación Nacional de Fabricantes Eléctricos de USA. Puede haber oficinas de normas locales o del gobierno que pueden ayudar a determinar cuales códigos y normas son necesarios para una instalación y operación segura.

Si no se siguen todos los códigos y normas aplicables, puede resultar en daños al equipo o lesiones serias a personas. No garantizamos los productos descritos en esta publicación para ser adecuados para su aplicación en particular, ni asumimos ninguna responsabilidad por el diseño de su producto, la instalación u operación.

Nuestros productos no son tolerantes a fallas y no han sido diseñados, fabricados o intencionados para uso o reventa como equipo de control en línea en ambientes peligrosos que requieren una ejecución sin fallas, tales como operación en instalaciones nucleares, sistemas de navegación aérea, o de comunicación, control de tráfico aéreo, máquinas de soporte de vida o sistemas de armamentos en las cuales la falla del producto puede resultar directamente en muerte, heridas personales, o daños físicos o ambientales severos ("Actividades de Alto Riesgo"). **Automationdirect.com** específicamente rechaza cualquier garantía ya sea expresada o implicada para actividades de alto riesgo.

Para información adicional acerca de garantía e información de seguridad, vea la sección de Términos y Condiciones de nuestro catálogo. Si tiene alguna pregunta sobre instalación u operación de este equipo, o si necesita información adicional, por favor llámenos al número 770-844-4200 en Estados Unidos.

Esta publicación está basada en la información disponible al momento de impresión. En **Automationdirect. com** nos esforzamos constantemente para mejorar nuestros productos y servicios, así que nos reservamos el derecho de hacer cambios al producto y/o a las publicaciones en cualquier momento sin notificación y sin ninguna obligación. Esta publicación también puede discutir características que no estén disponibles en ciertas revisiones del producto.

### **Marcas Registradas**

Esta publicación puede contener referencias a productos producidos y/u ofrecidos por otras compañías. Los nombres de las compañías y productos pueden tener marcas registradas y son propiedad única de sus respectivos dueños. Automationdirect.com, renuncia cualquier interés propietario en las marcas y nombres de otros.

### PROPIEDAD LITERARIA 2021, AUTOMATIONDIRECT.COM® INCORPORATED Todos los derechos reservados

No se permite copiar, reproducir, o transmitir de ninguna forma ninguna parte de este manual sin previo consentimiento por escrito de **Automationdirect.com**® **Incorprated**. **Automationdirect.com** retiene los derechos exclusivos a toda la información incluida en este documento. Los usuarios de este equipo pueden copiar este documento solamente para instalar, configurar y mantener el equipo correspondiente. También las instituciones de enseñanza pueden usar este manual para propósitos educativos.

# ~ AVERTISSEMENT ~

Nous vous remercions d'avoir acheté l'équipement d'automatisation de **Automationdirect.comMC**, en faisant des affaires comme, **AutomationDirect**. Nous tenons à ce que votre nouvel équipement d'automatisation fonctionne en toute sécurité. Toute personne qui installe ou utilise cet équipement doit lire la présente publication (et toutes les autres publications pertinentes) avant de l'installer ou de l'utiliser.

Afin de réduire au minimum le risque d'éventuels problèmes de sécurité, vous devez respecter tous les codes locaux et nationaux applicables régissant l'installation et le fonctionnement de votre équipement. Ces codes diffèrent d'une région à l'autre et, habituellement, évoluent au fil du temps. Il vous incombe de déterminer les codes à respecter et de vous assurer que l'équipement, l'installation et le fonctionnement sont conformes aux exigences de la version la plus récente de ces codes.

Vous devez, à tout le moins, respecter toutes les sections applicables du Code national de prévention des incendies, du Code national de l'électricité et des codes de la National Electrical Manufacturer's Association (NEMA). Des organismes de réglementation ou des services gouvernementaux locaux peuvent également vous aider à déterminer les codes ainsi que les normes à respecter pour assurer une installation et un fonctionnement sûrs.

L'omission de respecter la totalité des codes et des normes applicables peut entraîner des dommages à l'équipement ou causer de graves blessures au personnel. Nous ne garantissons pas que les produits décrits dans cette publication conviennent à votre application particulière et nous n'assumons aucune responsabilité à l'égard de la conception, de l'installation ou du fonctionnement de votre produit.

Nos produits ne sont pas insensibles aux défaillances et ne sont ni conçus ni fabriqués pour l'utilisation ou la revente en tant qu'équipement de commande en ligne dans des environnements dangereux nécessitant une sécurité absolue, par exemple, l'exploitation d'installations nucléaires, les systèmes de navigation aérienne ou de communication, le contrôle de la circulation aérienne, les équipements de survie ou les systèmes d'armes, pour lesquels la défaillance du produit peut provoquer la mort, des blessures corporelles ou de graves dommages matériels ou environnementaux («activités à risque élevé»). La société AutomationDirect nie toute garantie expresse ou implicite d'aptitude à l'emploi en ce qui a trait aux activités à risque élevé.

Pour des renseignements additionnels touchant la garantie et la sécurité, veuillez consulter la section Modalités et conditions de notre documentation. Si vous avez des questions au sujet de l'installation ou du fonctionnement de cet équipement, ou encore si vous avez besoin de renseignements supplémentaires, n'hésitez pas à nous téléphoner au 770-844-4200.

Cette publication s'appuie sur l'information qui était disponible au moment de l'impression. À la société AutomationDirect, nous nous efforçons constamment d'améliorer nos produits et services. C'est pourquoi nous nous réservons le droit d'apporter des modifications aux produits ou aux publications en tout temps, sans préavis ni quelque obligation que ce soit. La présente publication peut aussi porter sur des caractéristiques susceptibles de ne pas être offertes dans certaines versions révisées du produit.

### Marques de commerce

La présente publication peut contenir des références à des produits fabriqués ou offerts par d'autres entreprises. Les désignations des produits et des entreprises peuvent être des marques de commerce et appartiennent exclusivement à leurs propriétaires respectifs. AutomationDirect nie tout intérêt dans les autres marques et désignations.

Copyright 2021, Automationdirect.com Incorporated

Tous droits réservés

Nulle partie de ce manuel ne doit être copiée, reproduite ou transmise de quelque façon que ce soit sans le consentement préalable écrit de la société **Automationdirect.com Incorporated. AutomationDirect** conserve les droits exclusifs à l'égard de tous les renseignements contenus dans le présent document.

# **DL105 USER MANUAL**

Please include the Manual Number and the Manual Issue, both shown below, when communicating with Technical Support regarding this publication.

Manual Number: D1-USER-M

Issue: 3rd Edition, Rev. G

Issue Date: 07/21

| Publication History |       |                                                                           |

|---------------------|-------|---------------------------------------------------------------------------|

| Issue               | Date  | Description of Changes                                                    |

| Original            | 9/96  | Original issue                                                            |

| 2nd Edition         | 5/98  | Updated                                                                   |

| 2nd Edition, Rev. A | 7/03  | Updated with corrections and a new appendix                               |

| 3rd Edition         | 4/10  | Updated with corrections and added Appendix G                             |

| 3rd Edition, Rev. A | 12/18 | General updates. Converted to InDesign from Interleaf.                    |

| 3rd Edition, Rev. B | 02/20 | General updates.                                                          |

| 3rd Edition, Rev. C | 03/20 | Added note for F1-130-DD and F1-130-DD-D as obsoleted.                    |

| 3rd Edition, Rev. D | 10/20 | Added note for F1-130AA and F1-130AD as obsoleted                         |

| 3rd Edition, Rev. E | 05/20 | Added note for F1-130DR-D as obsoleted.                                   |

| 3rd Edition, Rev. F | 07/21 | Added note for F1-130AR as obsoleted.                                     |

| 3rd Edition, Rev. G | 07/21 | Added note for F1-130DR, B-F1130DR, F1-IOCON, and B-F1130AR as obsoleted. |

# **TABLE OF CONTENTS**

# **Chapter 1 - Getting Started**

| Introduction                                   |      |

|------------------------------------------------|------|

| The Purpose of this Manual                     | 1–2  |

| Where to Begin                                 | 1–2  |

| Supplemental Manuals                           |      |

| Technical Support                              | 1–2  |

| Conventions Used                               | 1–3  |

| Key Topics for Each Chapter                    | 1–3  |

| DL105 Micro PLC Components                     | 1–4  |

| The DL105 Micro PLC Family                     | 1–4  |

| Programming Methods                            | 1–5  |

| Direct SOFT Programming for Windows            | 1–5  |

| Handheld Programmer                            | 1–5  |

| I/O Quick Chart Selection                      | 1–6  |

| Quick Start for PLC Checkout and Programming   | 1–7  |

| Step 1: Unpack the Recommended DL105 Equipment | 1–7  |

| Step 2: Connect Switches to Input Terminals    |      |

| F1-130AR, F1-130AD, F1-130AA                   | 1–8  |

| F1-130DR, F1-130DD-D                           | 1–8  |

| Step 3: Connect the Power Wiring               | 1–9  |

| Step 4: Connect the Programming Device         | 1–9  |

| Step 5: Switch on the System Power             | 1–10 |

| Step 6: Initialize Scratchpad Memory           |      |

| Step 7: Enter a Ladder Program                 | 1–10 |

| Steps to Designing a Successful System         |      |

| Step 1: Review the Installation Guidelines     |      |

| Step 2: Understand PLC Setup Procedures        |      |

| Step 3: Review the I/O Selection Criteria      | 1–11 |

|                                                |      |

| Step 4: Choose a System Wiring Strategy                | 1–11           |

|--------------------------------------------------------|----------------|

| Step 5: Understand the System Operation                | 1–11           |

| Step 6: Review the Programming Concepts                |                |

| Step 7: Choose the Instructions                        | 1–12           |

| Step 8: Understand the Maintenance and Troubleshooting | Procedures1–12 |

| Questions and Answers about DL105 Micro PLCs           | 1–13           |

|                                                        |                |

| Chapter 2 –Installation, Wiring and Specif             | ications       |

| Safety Guidelines                                      | 2–2            |

| Plan for Safety                                        |                |

| Safety Techniques                                      |                |

| Three Levels of Protection                             | 2–3            |

| Emergency Stops                                        | 2–3            |

| Emergency Power Disconnect                             |                |

| Orderly System Shutdown                                | 2–4            |

| Class 1, Division 2 Approval                           | 2–4            |

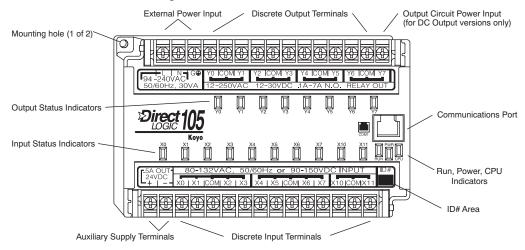

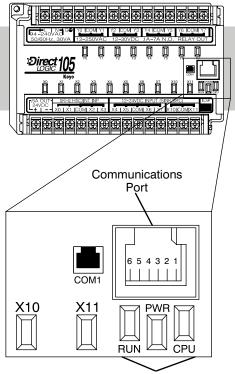

| Orientation to DL105 Front Panel                       | 2–5            |

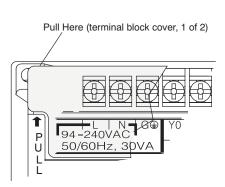

| Accessing the I/O Terminals                            | 2–5            |

| Protective Sheet for DL105 Vents                       | 2–6            |

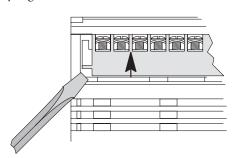

| Connector Removal                                      | 2–6            |

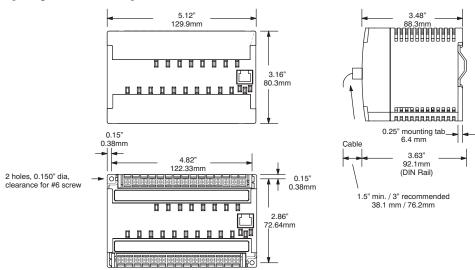

| Mounting Guidelines                                    | 2–7            |

| Unit Dimensions                                        |                |

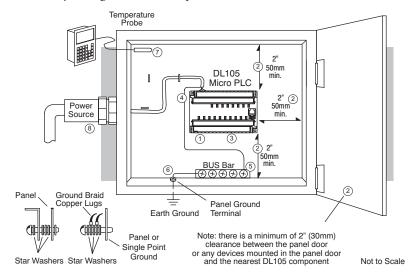

| Enclosures                                             | 2–7            |

| Panel Layout & Clearances                              | 2–8            |

| Agency Approvals                                       | 2–9            |

| Environmental Specifications                           | 2–9            |

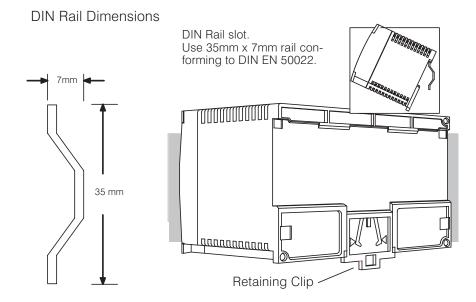

| Using Mounting Rails                                   | 2–10           |

| Wiring Guidelines                                      | 2–11           |

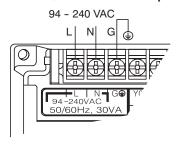

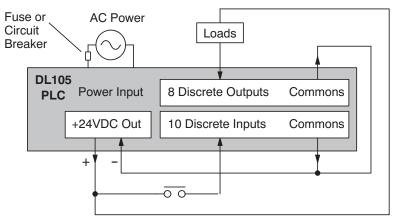

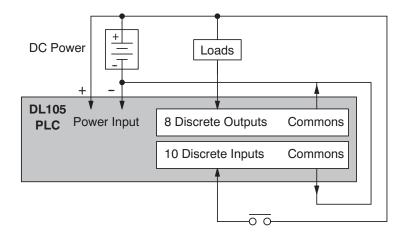

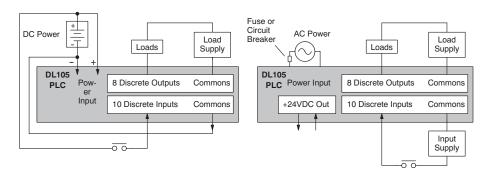

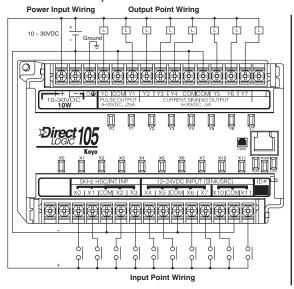

| Power Input Wiring                                     | 2–11           |

| Fuse Protection for Input Power                        | 2–11           |

| External Power Source                                  | 2–12           |

| Planning the Wiring Routes                             | 2–13           |

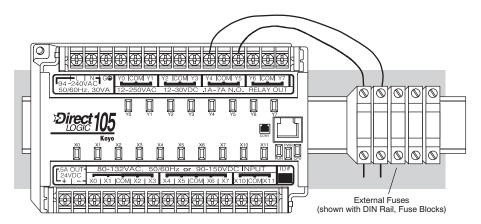

| Fuse Protection for Input and Output Circuits          | 2–13           |

| I/O Point Numbering                                    | 2–14           |

| System Wiring Strategies                          | 2–14 |

|---------------------------------------------------|------|

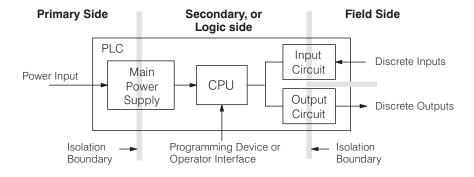

| PLC Isolation Boundaries                          | 2–14 |

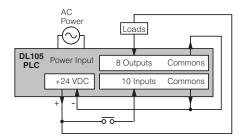

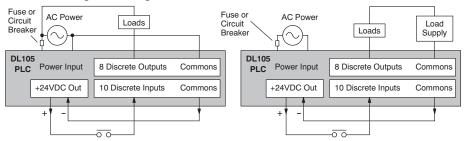

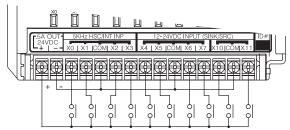

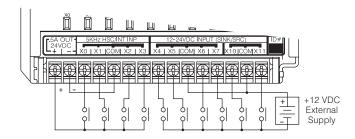

| Powering I/O Circuits with the Auxiliary Supply   | 2–16 |

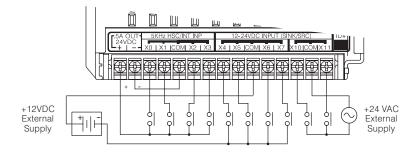

| Powering I/O Circuits Using Separate Supplies     | 2–17 |

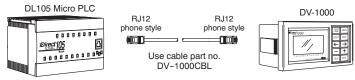

| Connecting Operator Interface Devices             | 2–18 |

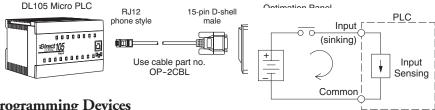

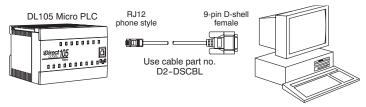

| Connecting Programming Devices                    | 2–18 |

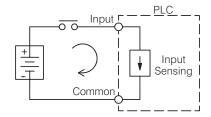

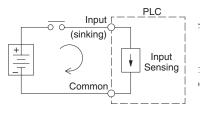

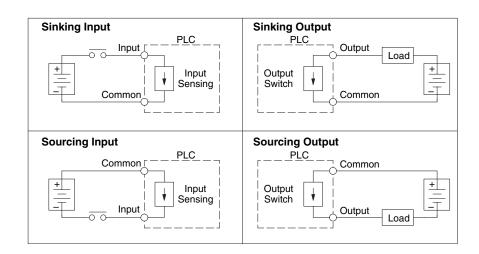

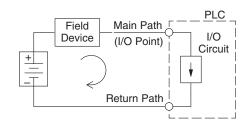

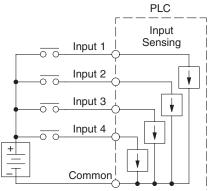

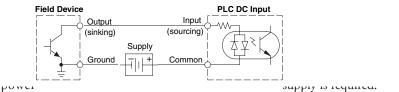

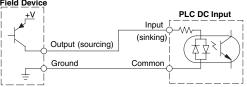

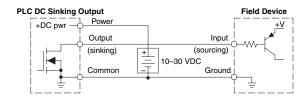

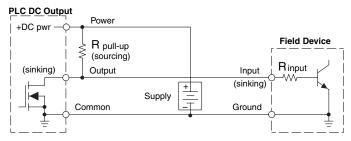

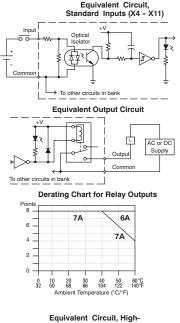

| Sinking / Sourcing Concepts                       | 2–19 |

| I/O "Common" Terminal Concepts                    | 2–20 |

| Connecting DC I/O to "Solid State" Field Devices  | 2–21 |

| Solid State Input Sensors                         | 2–21 |

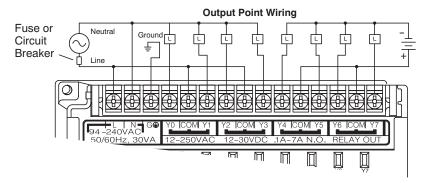

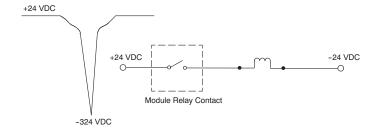

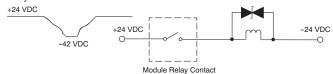

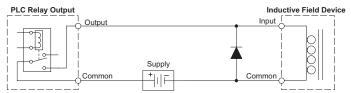

| Surge Suppression For Inductive Loads             | 2–24 |

| Prolonging Relay Contact Life                     | 2–25 |

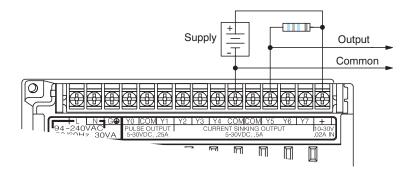

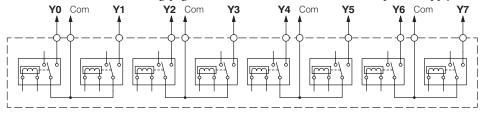

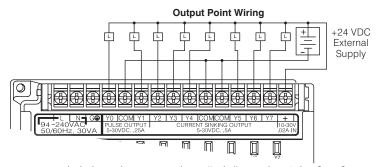

| DC Output Wiring Methods                          | 2–27 |

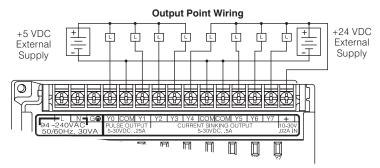

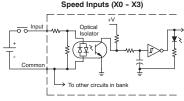

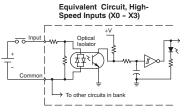

| High-Speed I/O Wiring Methods                     | 2–28 |

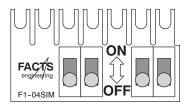

| F1-04SIM Input Simulator Wiring                   | 2–29 |

| Wiring Diagrams and Specifications                | 2–30 |

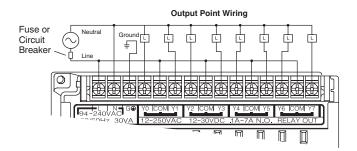

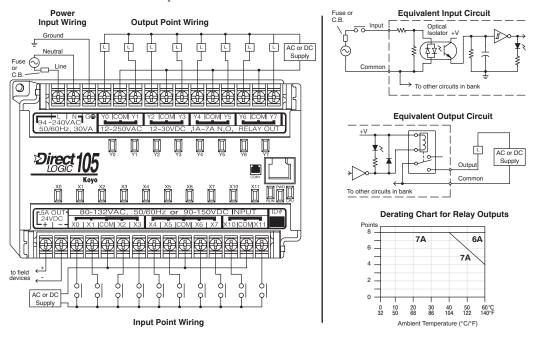

| F1–130AR I/O Wiring Diagram                       | 2–30 |

| Auxiliary +24V Power Supply                       | 2–31 |

| F1-130AR General Specifications                   | 2–31 |

| F1-130AR Relay Output Specifications              | 2–32 |

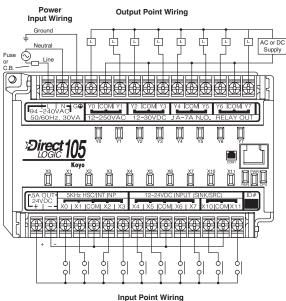

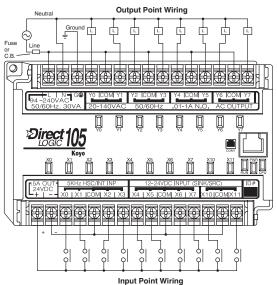

| F1-130DR/ F1-130DR-CE I/O Wiring Diagram          | 2–33 |

| Auxiliary +24V Power Supply                       | 2–34 |

| F1-130DR/ F1-130DR-CE Relay Output Specifications | 2–35 |

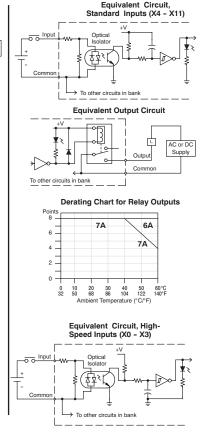

| F1–130AD I/O Wiring Diagram                       | 2–36 |

| Auxiliary +24V Power Supply                       | 2–36 |

| F1–130AD General Specifications                   | 2–37 |

| F1-130AD I/O DC Output Specifications             | 2–38 |

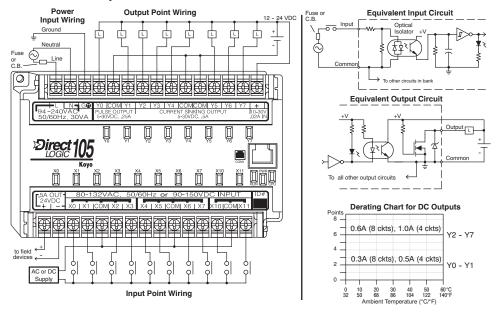

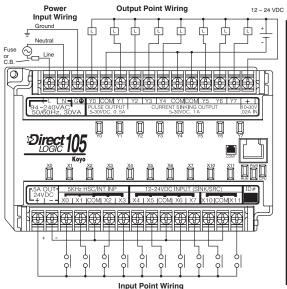

| F1-130DD/ F1-130DD-CE I/O Wiring Diagram          | 2–39 |

| Auxiliary +24V Power Supply                       | 2–39 |

| F1–130DD/ F130–DD–CE General Specifications       | 2–40 |

| F1-130DD/ F130-DD-CE DC Output Specifications     |      |

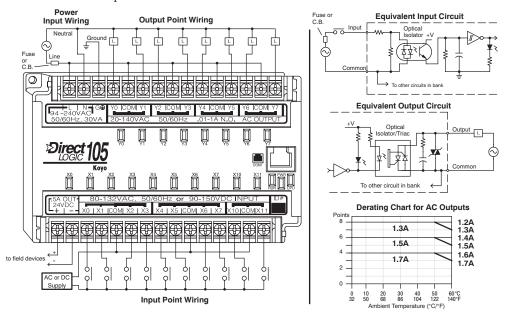

| F1–130AA I/O Wiring Diagram                       | 2–42 |

| Auxiliary +24V Power Supply                       | 2–42 |

| F1-130AA General Specifications                   | 2–43 |

| F1–130AA I/O DC Output Specifications             |      |

| F1–130DA I/O Wiring Diagram                       | 2–45 |

| Auxiliary +24V Power Supply                          | 2–45     |

|------------------------------------------------------|----------|

| F1–130DA General Specifications                      | 2–46     |

| F1–130DA AC Output Specifications                    | 2–47     |

| F1-130DR-D I/O Wiring Diagram                        | 2–48     |

| No Auxiliary +24V Power Supply                       | 2–48     |

| F1-130DR-D General Specifications                    | 2–49     |

| F1-130DR/ F1-130DR-CE Relay Output Specifications    | 2–50     |

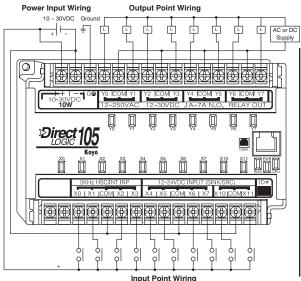

| F1-130DD-D I/O Wiring Diagram                        | 2–51     |

| No Auxiliary +24V Power Supply                       | 2–51     |

| F1-130DD-D General Specifications                    | 2–52     |

| F1-130DD-D DC Output Specifications                  | 2–53     |

| Glossary of Specification Terms                      | 2–54     |

|                                                      |          |

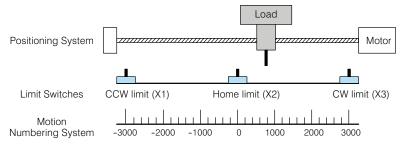

| <b>Chapter 3 - High-Speed Input and Pulse Output</b> | Features |

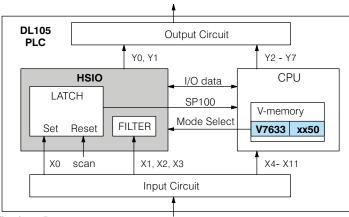

| Introduction                                         | 3–2      |

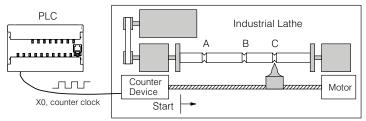

| Built-in Motion Control Solution                     | 3–2      |

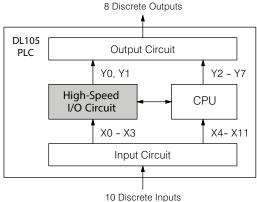

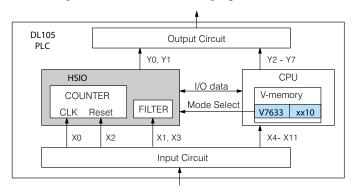

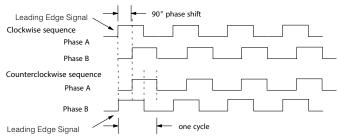

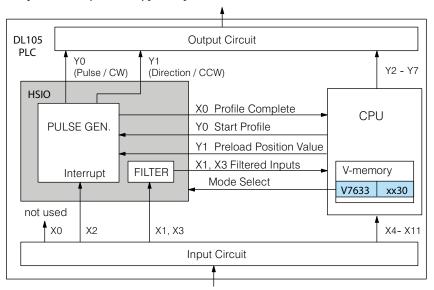

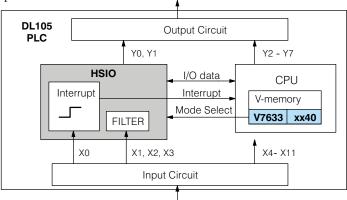

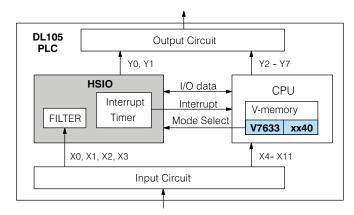

| Dedicated High- Speed I/O Circuit                    | 3–3      |

| Wiring Diagrams for Each HSIO Mode                   | 3–3      |

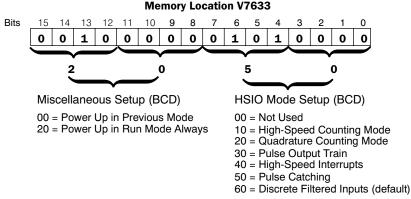

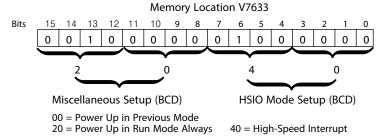

| Choosing the HSIO Operating Mode                     | 3–4      |

| Understanding the Six Modes                          | 3–4      |

| Default Mode                                         | 3–4      |

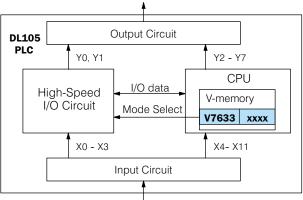

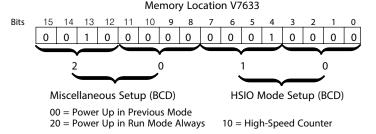

| Configuring the HSIO Mode                            | 3–5      |

| Configuring Inputs X0–X3                             |          |

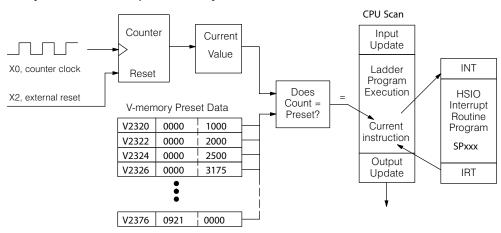

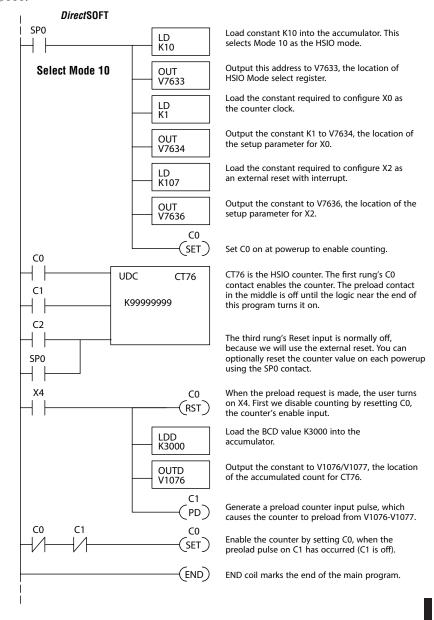

| Mode 10: High-Speed Counter                          | 3–6      |

| Purpose                                              | 3–6      |

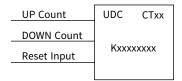

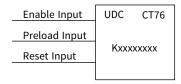

| Functional Block Diagram                             | 3-6      |

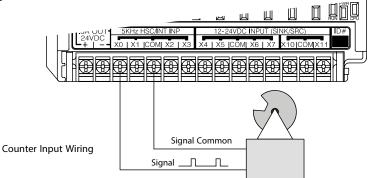

| Wiring Diagram                                       | 3–7      |

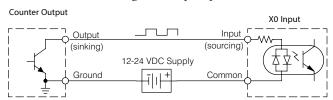

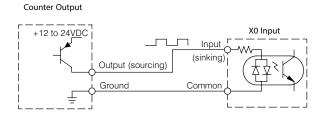

| Interfacing to Counter Outputs                       | 3–7      |

| Setup for Mode 10                                    | 3–8      |

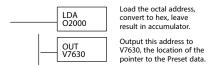

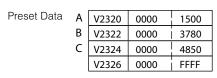

| Preset Data Starting Location                        | 3–9      |

| Using Fewer than 24 Presets                          | 3–9      |

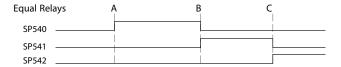

| Equal Relay Numbers                                  | 3–9      |

| Calculating Your Preset Values                       |          |

| X Input Configuration                                | 3–10     |

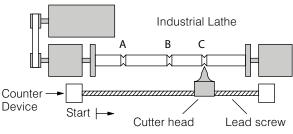

| Writing Your Control Program                         | 3–11     |

|                                                      |          |

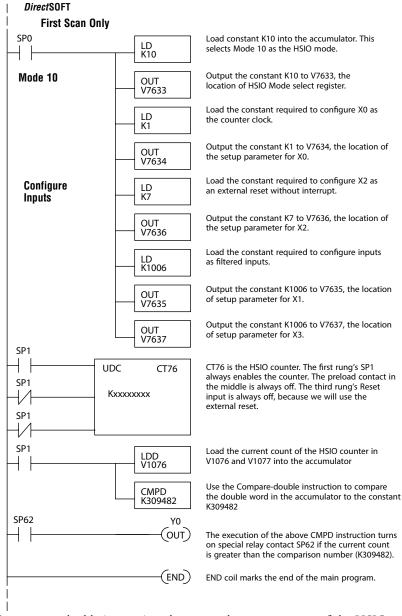

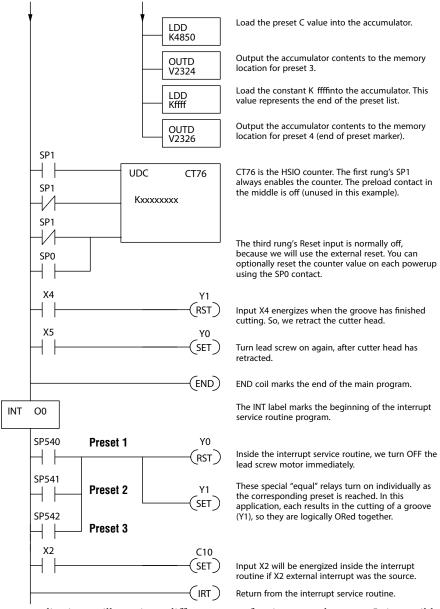

|     | Program Example: Counter Without Preset       | 3–11 |

|-----|-----------------------------------------------|------|

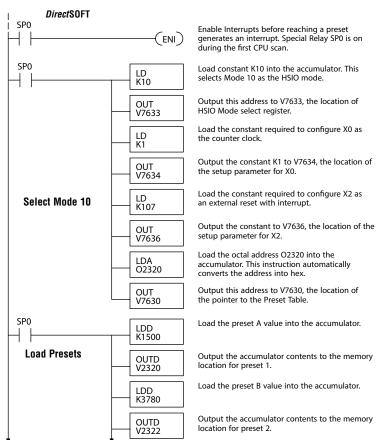

|     | Counter With Presets Program Example          | 3–13 |

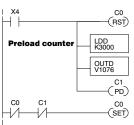

|     | Counter With Preload Program Example          | 3–15 |

|     | Troubleshooting Guide for Mode 10             | 3–16 |

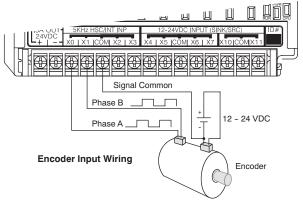

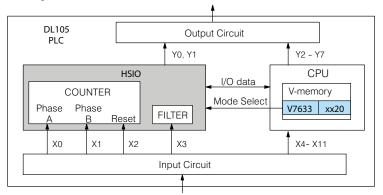

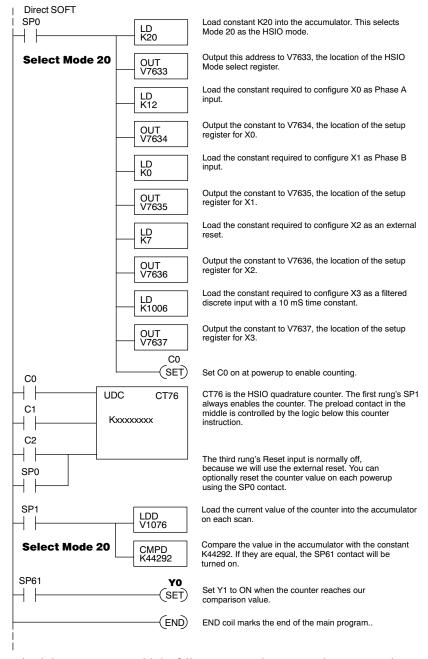

| V   | 1ode 20: Quadrature Counter                   | 3–17 |

|     | Purpose                                       | 3–17 |

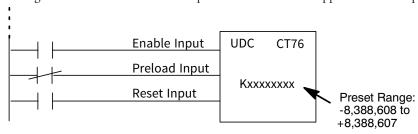

|     | Functional Block Diagram                      | 3–17 |

|     | Quadrature Encoder Signals                    | 3–17 |

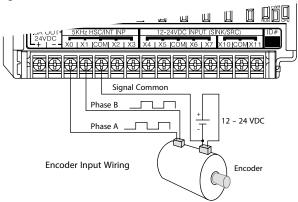

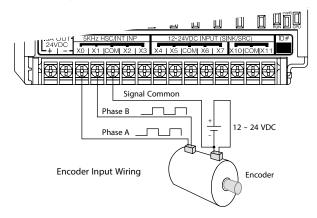

|     | Wiring Diagram                                |      |

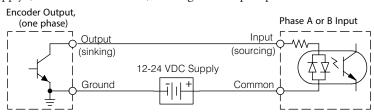

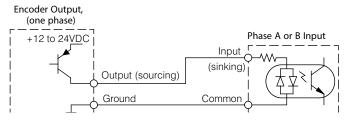

|     | Interfacing to Encoder Outputs                | 3–18 |

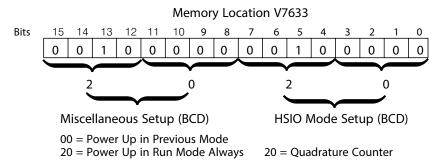

|     | Setup for Mode 20                             | 3–19 |

|     | X Input Configuration                         | 3–19 |

|     | Writing Your Control Program                  | 3–20 |

|     | Quadrature Counter w/Preload Program Example  | 3–20 |

|     | Counter Preload Program Example               |      |

|     | Troubleshooting Guide for Mode 20             | 3–22 |

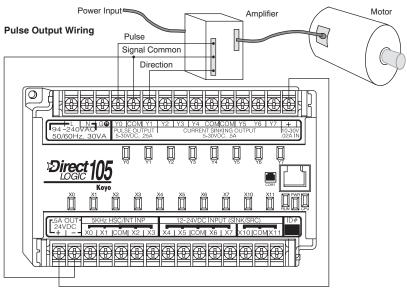

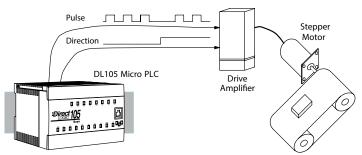

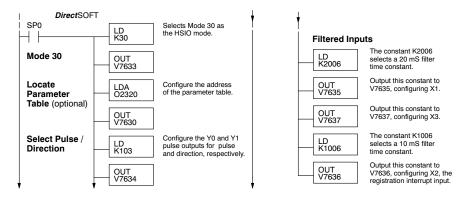

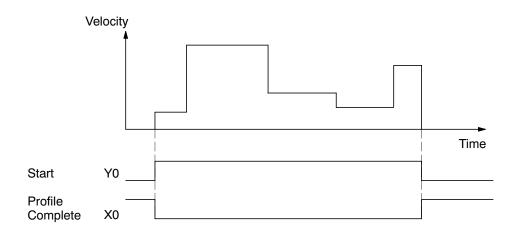

| V   | 1ode 30: Pulse Output                         | 3–23 |

|     | Functional Block Diagram                      |      |

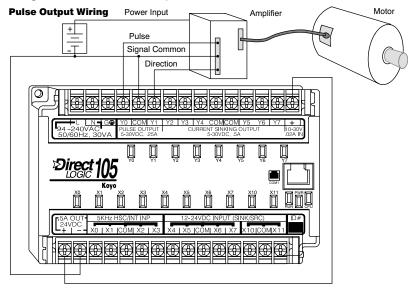

|     | Wiring Diagram                                |      |

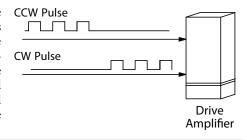

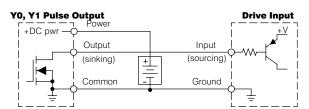

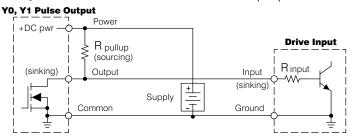

|     | Interfacing to Drive Inputs                   |      |

|     | Motion Profile Specifications                 |      |

|     | Physical I/O Configuration                    | 3–26 |

|     | Logical I/O Functions                         |      |

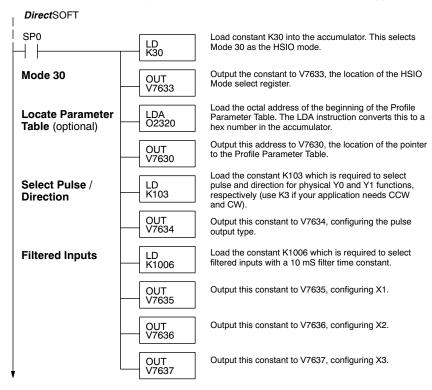

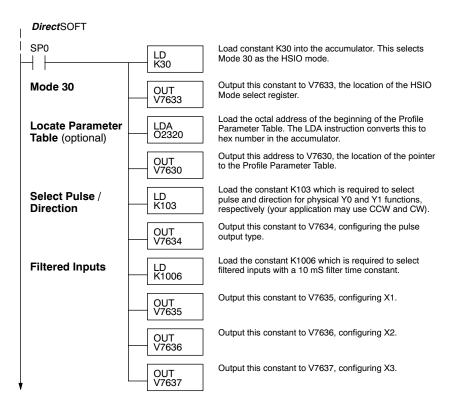

|     | Setup for Mode 30                             | 3–27 |

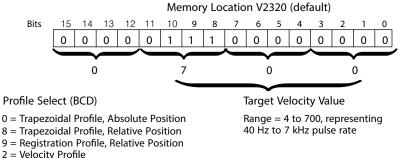

|     | Profile / Velocity Select Register            | 3–27 |

|     | Profile Parameter Table                       | 3–28 |

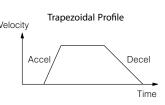

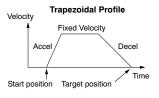

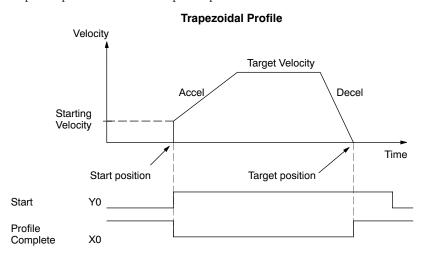

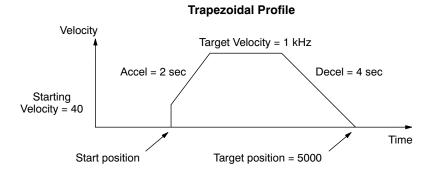

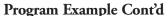

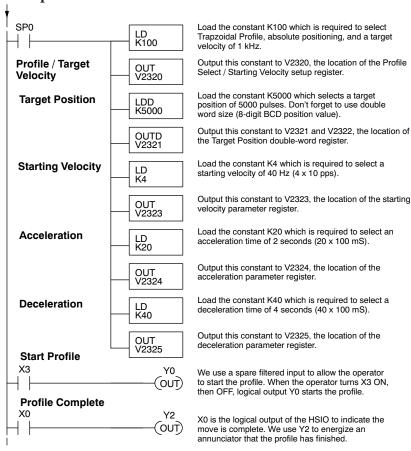

|     | Trapezoidal Profile                           | 3–28 |

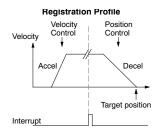

|     | Registration Profile                          | 3–28 |

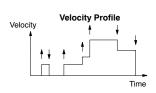

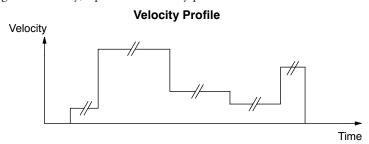

|     | Velocity Profile                              | 3–28 |

|     | Choosing the Profile Type                     | 3–29 |

|     | Trapezoidal Profile Defined                   |      |

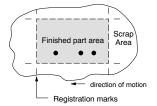

|     | Registration and Home Search Profiles Defined | 3–29 |

|     | Velocity Profile Defined                      |      |

| T   | rapezoidal Profile Operation                  |      |

| - ' | Trapezoidal Profile Applications              |      |

|     | Trapezoidal Profile Program Example           |      |

|     |                                               |      |

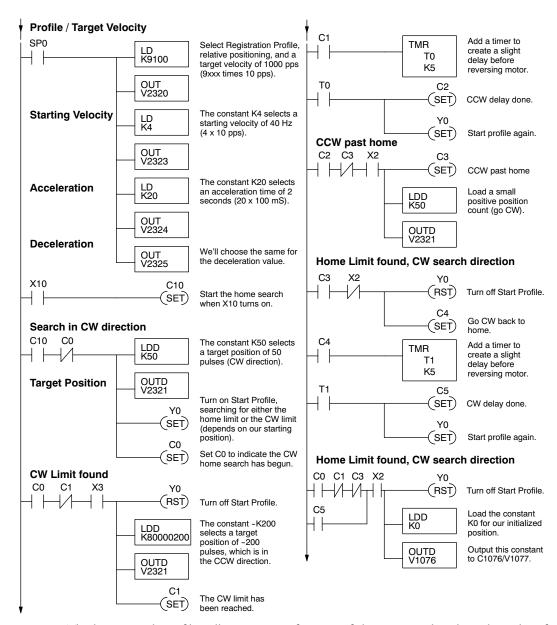

| Registration Profile Operation               |      |

|----------------------------------------------|------|

| Registration Applications                    | 3–33 |

| Registration Profile Program Example         | 3–34 |

| Home Search Program Example                  | 3–36 |

| Velocity Profile Operation                   | 3–38 |

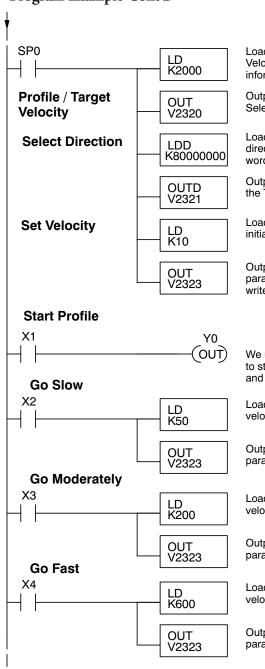

| Velocity Profile Program Example             | 3–39 |

| Pulse Output Error Codes                     | 3–41 |

| Troubleshooting Guide for Mode 30            |      |

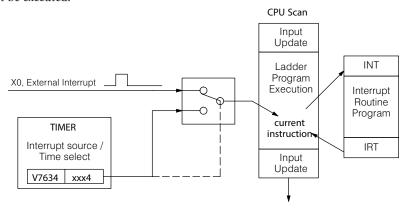

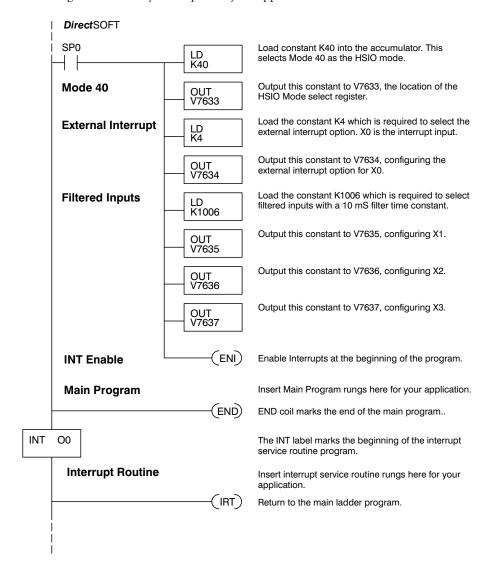

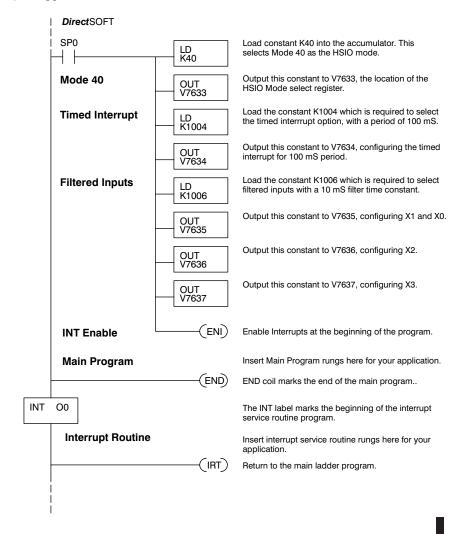

| Mode 40: High-Speed Interrupts               | 3–43 |

| Setup for Mode 40                            | 3–44 |

| Interrupts and the Ladder Program            | 3–44 |

| External Interrupt Timing Parameters         | 3–45 |

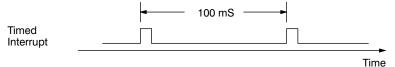

| Timed Interrupt Parameters                   | 3–45 |

| X Input / Timed INT Configuration            | 3–45 |

| External Interrupt Program Example           | 3–46 |

| Timed Interrupt Program Example              | 3–47 |

| Mode 50: Pulse Catch Input                   | 3–48 |

| Purpose                                      |      |

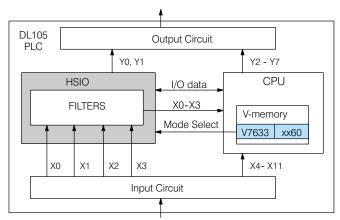

| Functional Block Diagram                     | 3–48 |

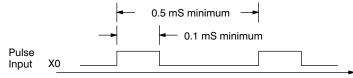

| Pulse Catch Timing Parameters                |      |

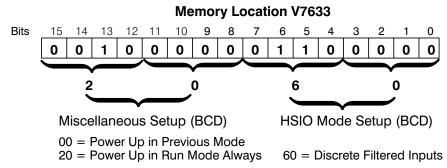

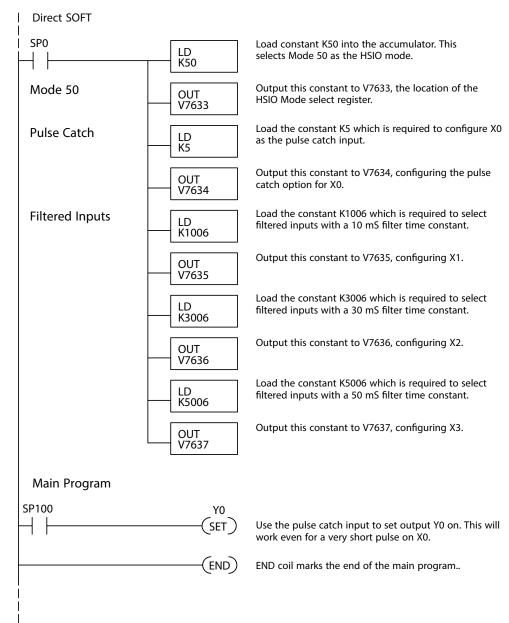

| Setup for Mode 50                            | 3–49 |

| X Input Configuration                        | 3–49 |

| Pulse Catch Program Example                  |      |

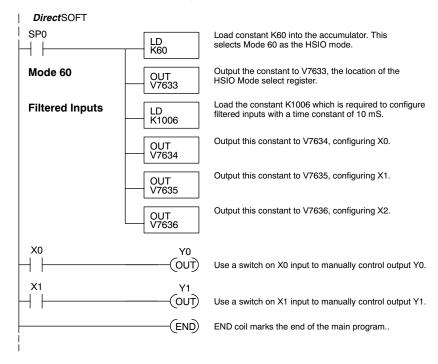

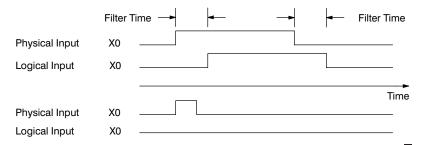

| Mode 60: Discrete Inputs with Filter         | 3–51 |

| Purpose                                      | 3–51 |

| Functional Block Diagram                     |      |

| Input Filter Timing Parameters               |      |

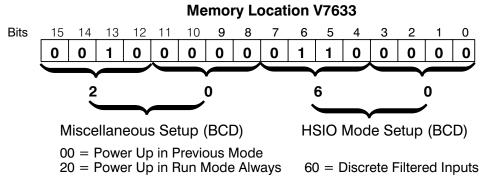

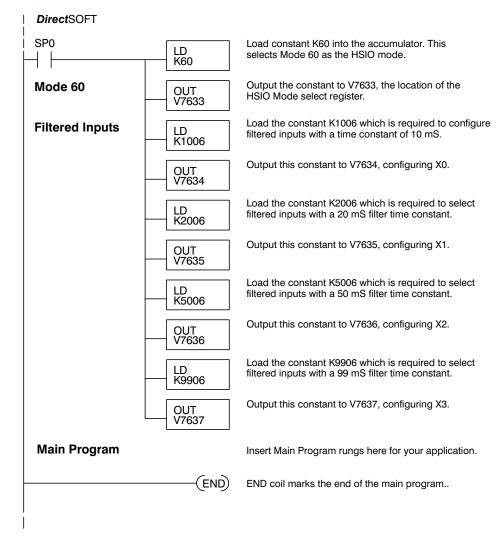

| Setup for Mode 60                            |      |

| X Input Configuration                        |      |

| Filtered Inputs Program Example              | 3–53 |

| Chapter 4 CDII Specifications and Operation  |      |

| Chapter 4 - CPU Specifications and Operation | _    |

| Introduction                                 |      |

| DL105 CPU Features                           |      |

| CPU Specifications                           | 4–3  |

| CPU Hardware Setup                          | 4_4  |

|---------------------------------------------|------|

| Communication Port Pinout Diagrams          |      |

| Connecting the Programming Devices          |      |

| CPU Setup Information                       |      |

| CPU Modes                                   |      |

| Mode of Operation at Power-up               |      |

| Changing Modes in the DL105 PLC             |      |

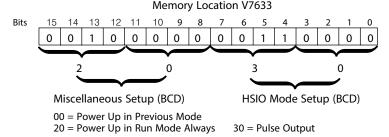

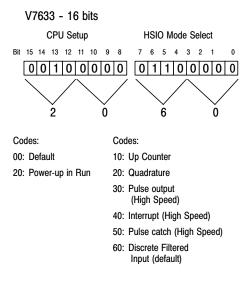

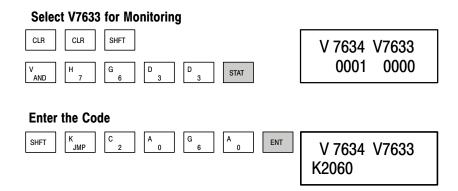

| Setting Bits in V7633                       |      |

| Auxiliary Functions                         | 4–8  |

| Clearing an Existing Program                | 4–9  |

| Initializing System Memory                  | 4–9  |

| Setting Retentive Memory Ranges             | 4–9  |

| Using a Password                            | 4–10 |

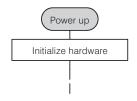

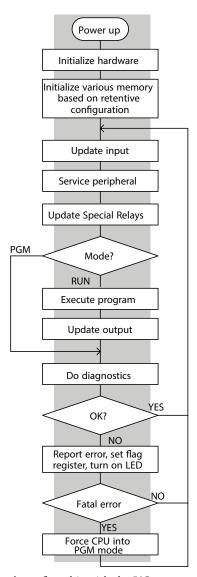

| CPU Operating System                        | 4–11 |

| Program Mode                                | 4–12 |

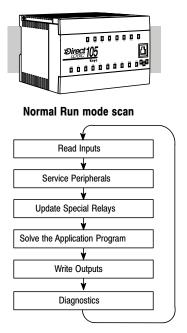

| Run Mode                                    | 4–12 |

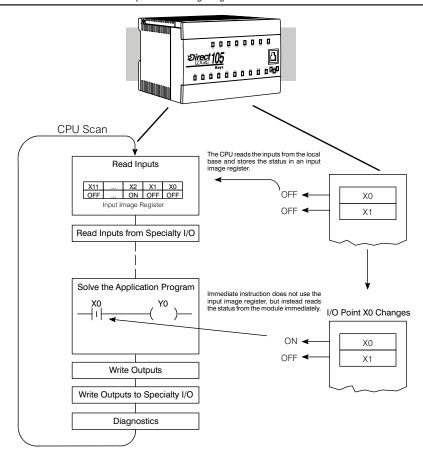

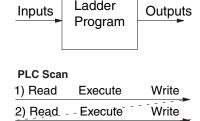

| Read Inputs                                 | 4–13 |

| Service Peripherals and Force I/O           | 4–13 |

| Update Special Relays and Special Registers | 4–13 |

| Solve Application Program                   | 4–14 |

| Write Outputs                               | 4–14 |

| Diagnostics                                 | 4–14 |

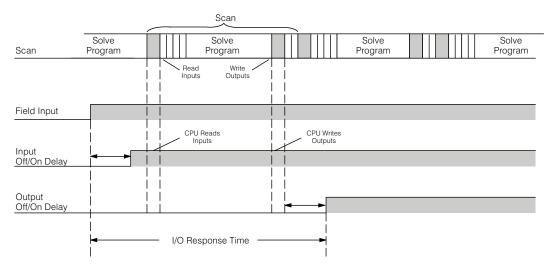

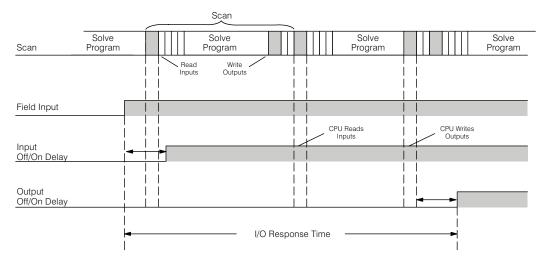

| I/O Response Time                           | 4–15 |

| Is Timing Important for Your Application?   | 4–15 |

| Normal Minimum I/O Response                 | 4–15 |

| Normal Maximum I/O Response                 | 4–16 |

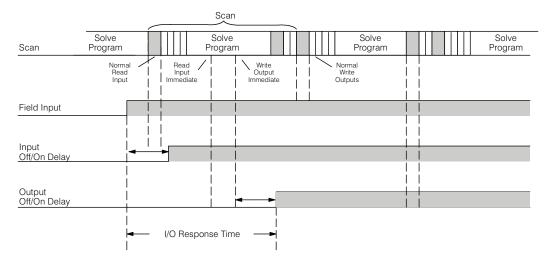

| Improving Response Time                     | 4–17 |

| CPU Scan Time Considerations                | 4–18 |

| Reading Inputs                              | 4–18 |

| Writing Outputs                             |      |

| Application Program Execution               | 4–19 |

| PLC Numbering Systems                       | 4–20 |

| PLC Resources                               |      |

| V- Memory                                   |      |

| Binary-Coded Decimal Numbers                |      |

| Hexadecimal Numbers                         | 4_21 |

### **Table of Contents**

| Memory Map                                                 | 4–22 |

|------------------------------------------------------------|------|

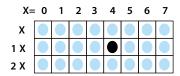

| Octal Numbering System                                     | 4–22 |

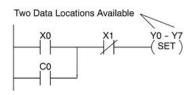

| Discrete and Word Locations                                | 4–22 |

| V-memory Locations for Discrete Memory Areas               | 4–22 |

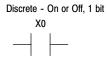

| Input Points (X Data Type)                                 | 4–23 |

| Output Points (Y Data Type)                                | 4–23 |

| Control Relays (C Data Type)                               | 4–23 |

| Timers and Timer Status Bits (T Data type)                 | 4–23 |

| Timer Current Values (V Data Type)                         | 4–24 |

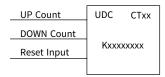

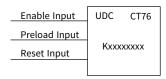

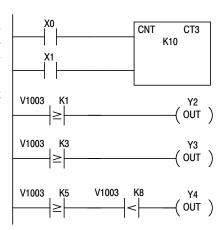

| Counters and Counter Status Bits (CT Data type)            | 4–24 |

| Counter Current Values (V Data Type)                       | 4–24 |

| Word Memory (V Data Type)                                  | 4–25 |

| Stages (S Data type)                                       | 4–25 |

| Special Relays (SP Data Type)                              | 4–25 |

| DL105 System V-memory                                      | 4–26 |

| System Parameters and Default Data Locations (V Data Type) | 4–26 |

| DL105 Aliases                                              | 4–28 |

| DL105 Memory Map                                           | 4–29 |

| X Input Bit Map                                            | 4–30 |

| Y Output Bit Map                                           | 4–30 |

| Control Relay Bit Map                                      | 4–30 |

| Stage Control / Status Bit Map                             | 4–31 |

| Timer Status Bit Map                                       | 4–31 |

| Counter Status Bit Map                                     | 4–32 |

| Chapter 5 - Standard RLL Instructions                      |      |

| •                                                          |      |

| Introduction                                               |      |

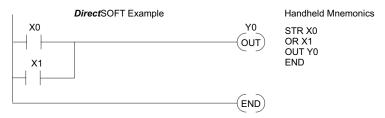

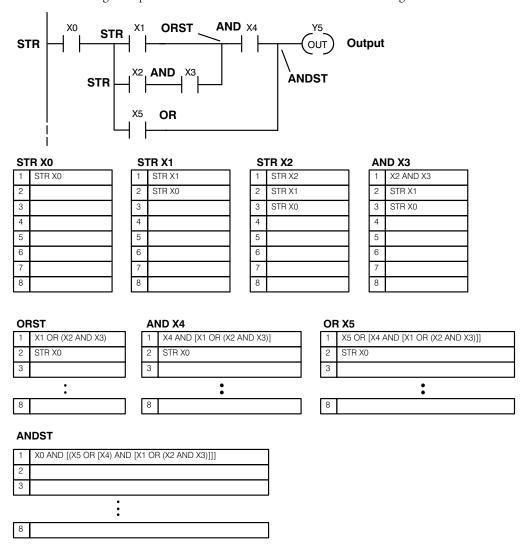

| Using Boolean Instructions                                 |      |

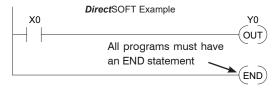

| END Statement                                              |      |

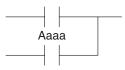

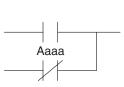

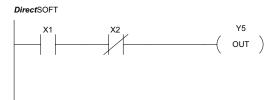

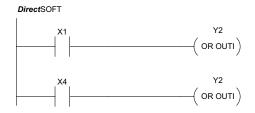

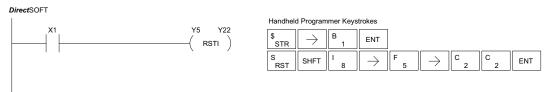

| Simple Rungs                                               |      |

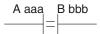

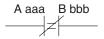

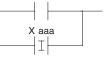

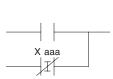

| Normally Closed Contact                                    |      |

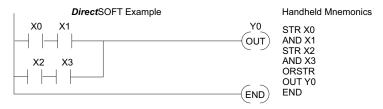

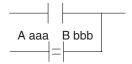

| Contacts in Series                                         | 5-5  |

| Mid-line Outputs                                      | 5-5  |

|-------------------------------------------------------|------|

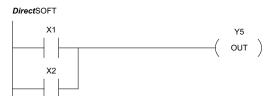

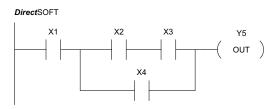

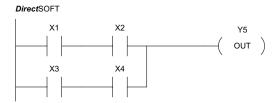

| Parallel Elements                                     | 5-6  |

| Joining Series Branches in Parallel                   | 5-6  |

| Joining Parallel Branches in Series                   | 5-6  |

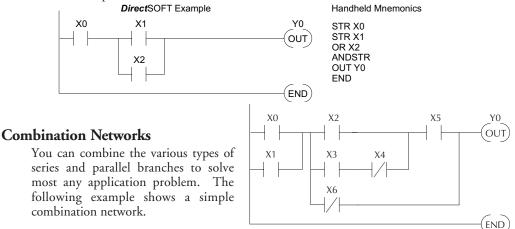

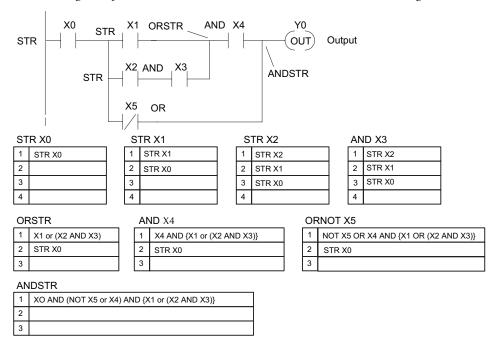

| Combination Networks                                  | 5-6  |

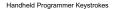

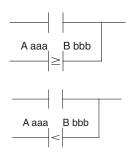

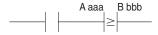

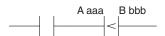

| Comparative Boolean                                   | 5-7  |

| Boolean Stack                                         | 5-7  |

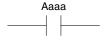

| Immediate Boolean                                     | 5-8  |

| Boolean Instructions                                  | 5-9  |

| Comparative Boolean                                   |      |

| mmediate Instructions                                 | 5-24 |

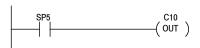

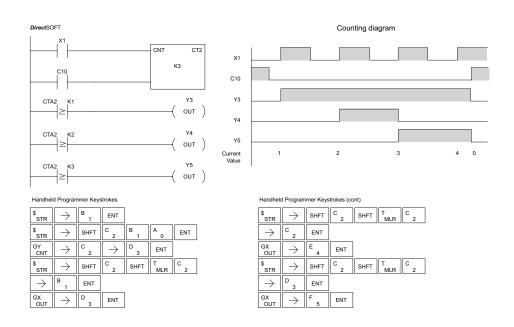

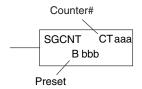

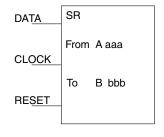

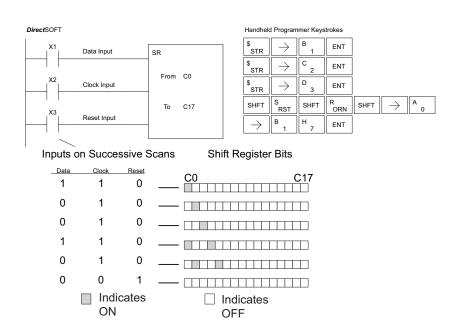

| Timer, Counter and Shift Register Instructions        | 5-29 |

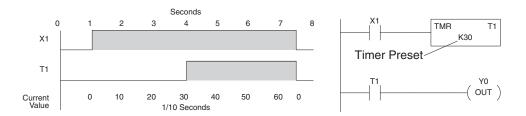

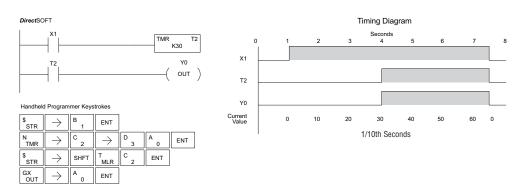

| Using Timers                                          |      |

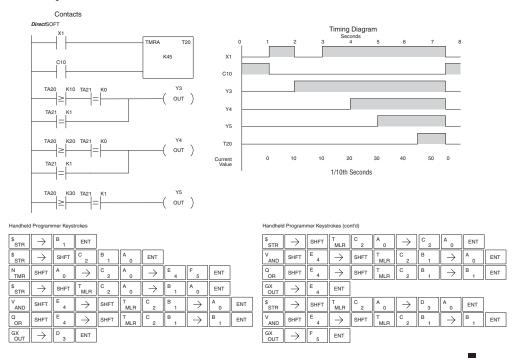

| Timer Example Using Discrete Status Bits              | 5-31 |

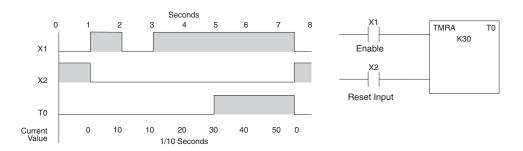

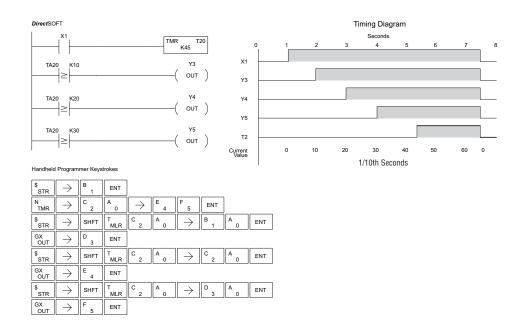

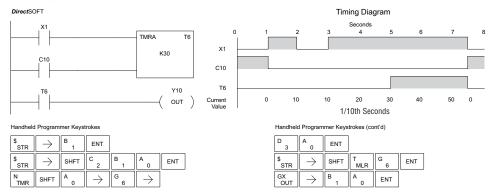

| Accumulating Timer (TMRA)                             | 5-32 |

| Accumulating Timer Example using Discrete Status Bits | 5-33 |

| Accumulator Timer Example Using Comparative Contacts  |      |

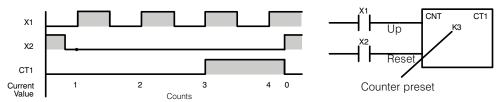

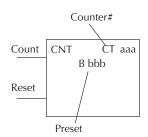

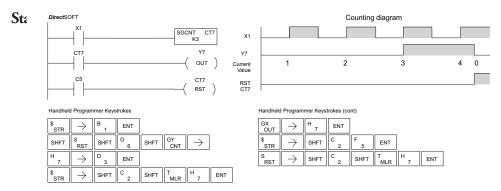

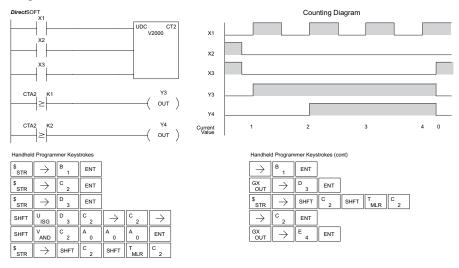

| Counter Example Using Discrete Status Bits            | 5-36 |

| Counter Example Using Comparative Contacts            |      |

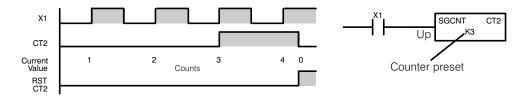

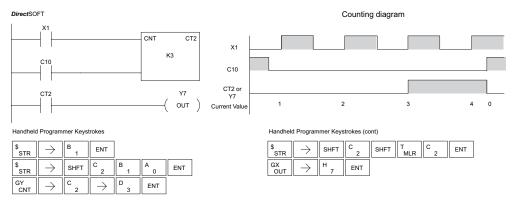

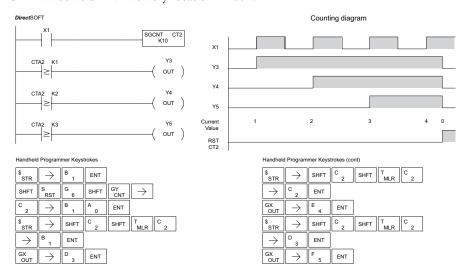

| Stage Counter Example Using Discrete Status Bits      |      |

| Stage Counter Example Using Comparative Contacts      | 5-38 |

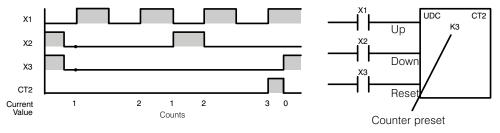

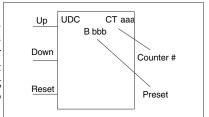

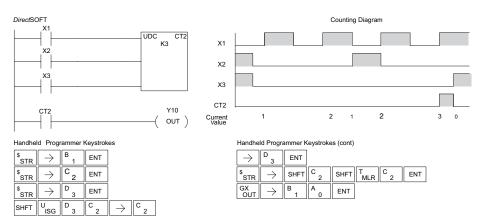

| Up/Down Counter Example Using Discrete Status Bits    | 5-40 |

| Up/Down Counter Example Using Comparative Contacts    | 5-40 |

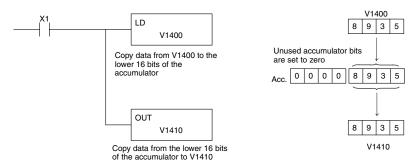

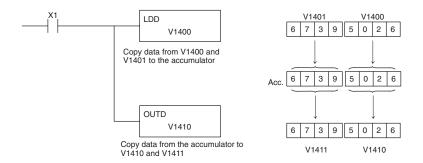

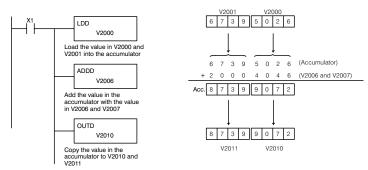

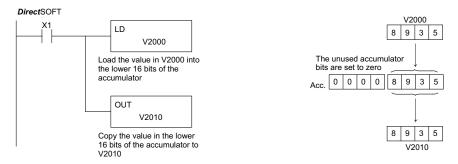

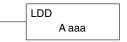

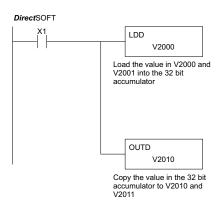

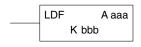

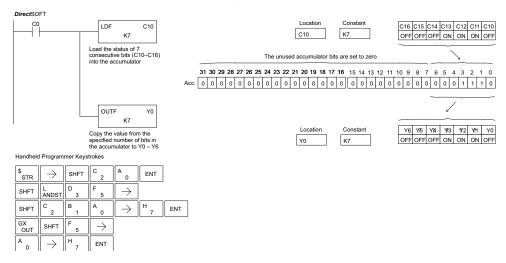

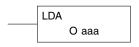

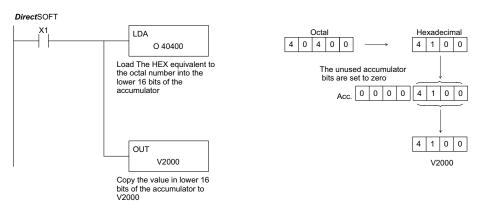

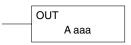

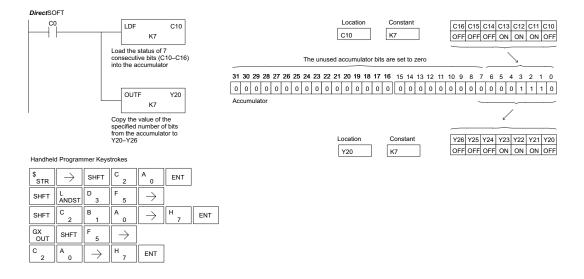

| Accumulator/Stack Load and Output Data Instructions   |      |

| Using the Accumulator                                 |      |

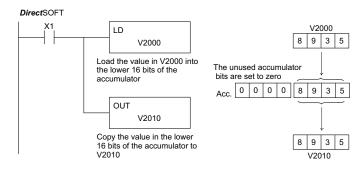

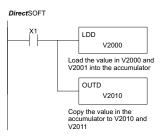

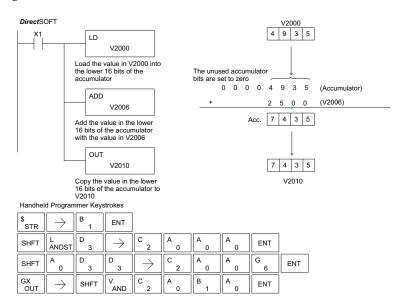

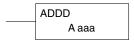

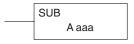

| Copying Data to the Accumulator                       | 5-42 |

| Changing the Accumulator Data                         | 5-43 |

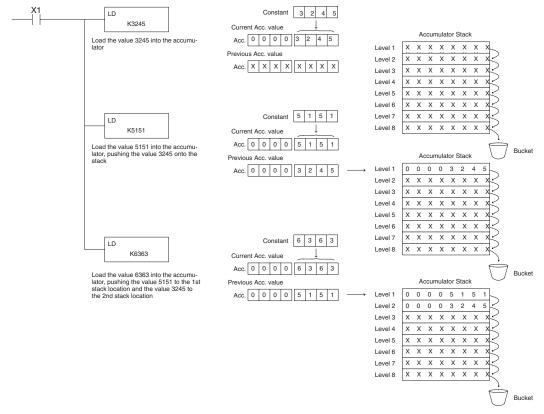

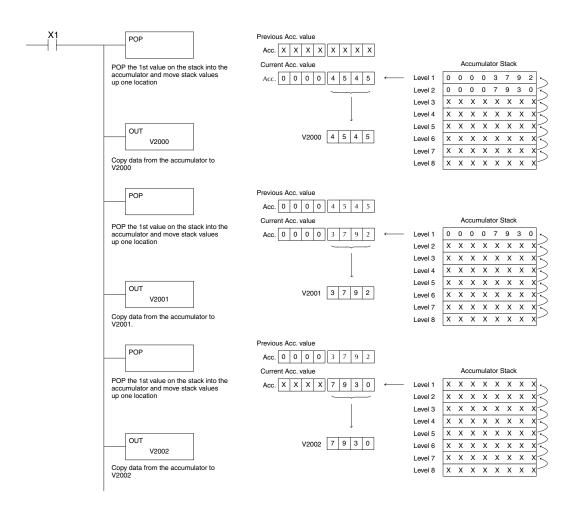

| Using the Accumulator Stack                           |      |

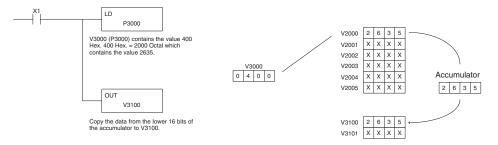

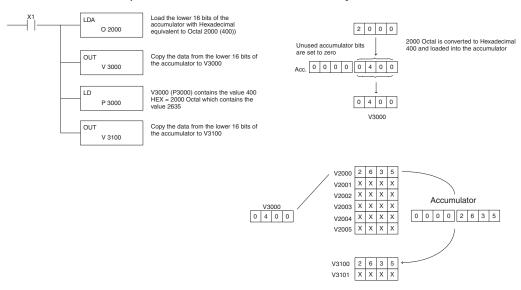

| Using Pointers                                        | 5-46 |

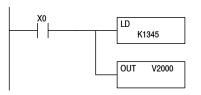

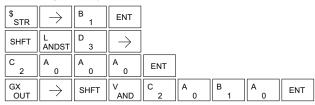

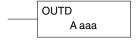

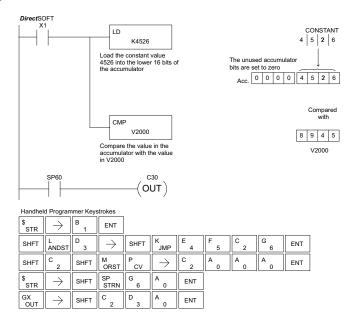

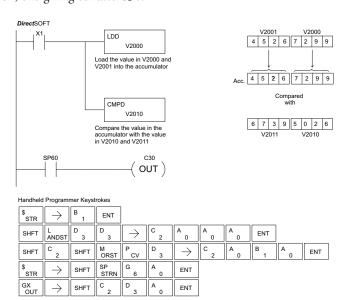

| Load (LD)                                             | 5-47 |

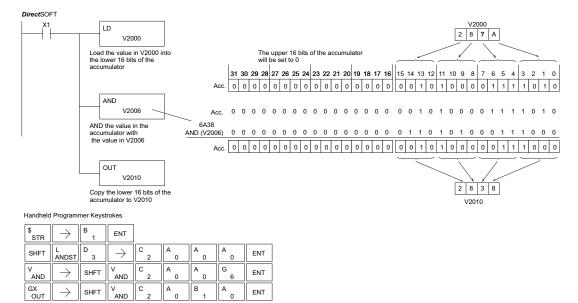

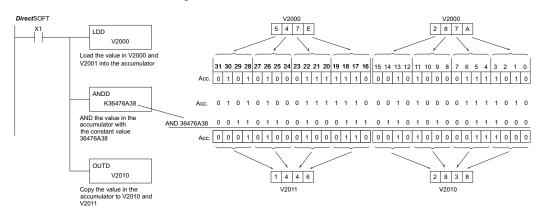

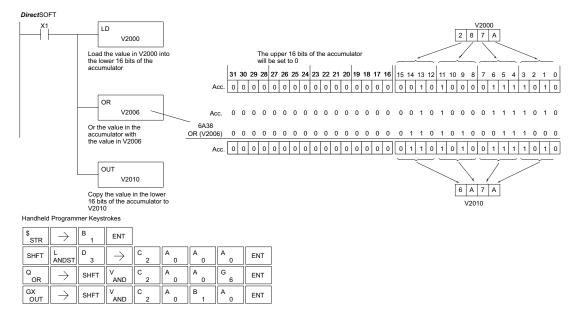

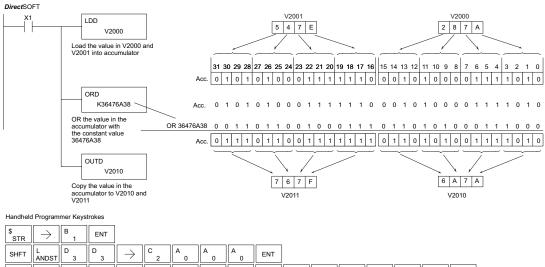

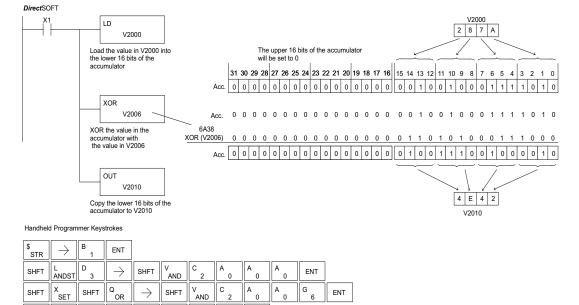

| Logical Instructions (Accumulator)                    | 5-55 |

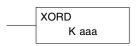

| Exclusive OR Double (XORD)                            | 5-60 |

| Math Instructions                                     | 5-63 |

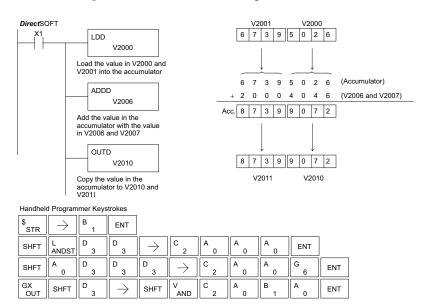

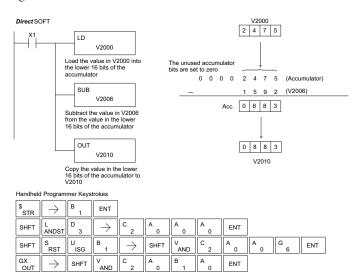

| Subtract (SUB)                                        | 5-65 |

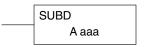

| Subtract Double (SUBD)                       | 5-66 |

|----------------------------------------------|------|

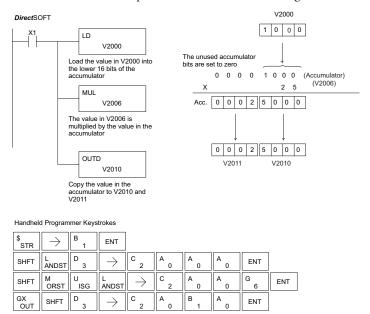

| Multiply (MUL)                               | 5-67 |

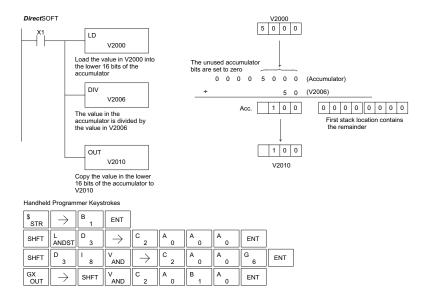

| Divide (DIV)                                 | 5-68 |

| Increment Binary (INCB)                      | 5-69 |

| Decrement Binary (DECB)                      | 5-69 |

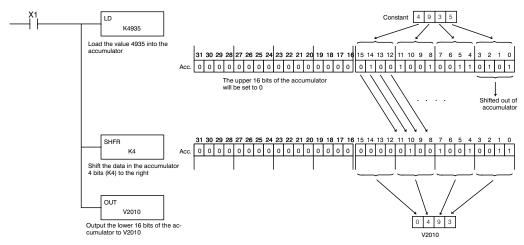

| Bit Operation Instructions                   | 5-70 |

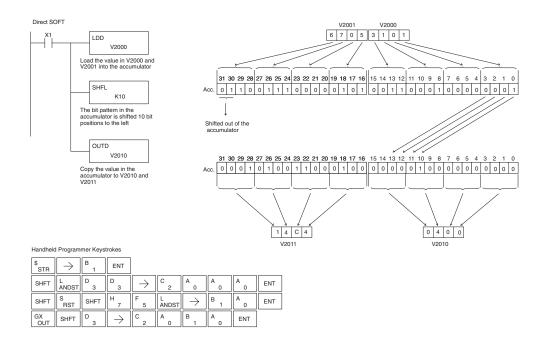

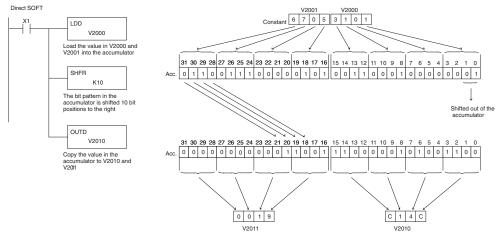

| Shift Left (SHFL)                            | 5-70 |

| Shift Right (SHFR)                           | 5-71 |

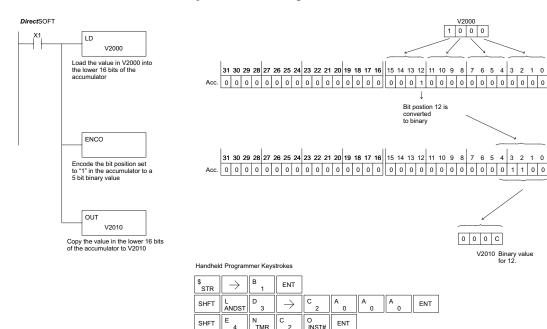

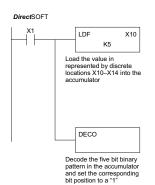

| Encode (ENCO)                                | 5-72 |

| Decode (DECO)                                | 5-73 |

| Number Conversion Instructions (Accumulator) | 5-74 |

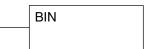

| Binary (BIN)                                 |      |

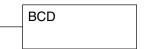

| Binary Coded Decimal (BCD)                   | 5-75 |

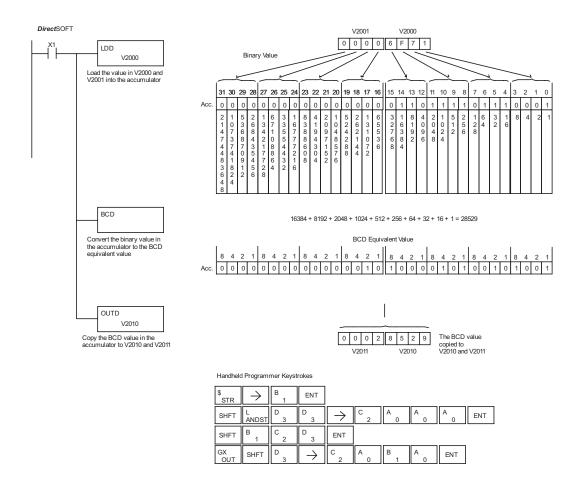

| Invert (INV)                                 | 5-76 |

| Table Instructions                           | 5-77 |

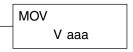

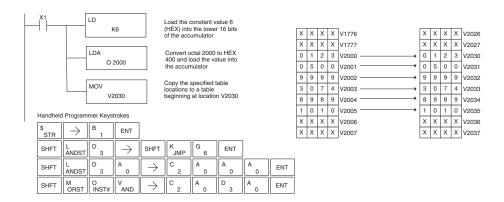

| Move (MOV)                                   | 5-77 |

| Move Memory Cartridge (MOVMC)                | 5-78 |

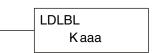

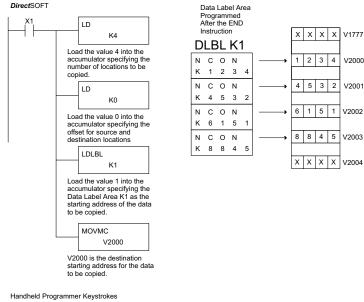

| Load Label (LDLBL)                           | 5-78 |

| Copy Data From a Data Label Area to V-Memory | 5-79 |

| CPU Control Instructions                     | 5-80 |

| No Operation (NOP)                           | 5-80 |

| End (END)                                    | 5-80 |

| Stop (STOP)                                  | 5-80 |

| Program Control Instructions                 | 5-81 |

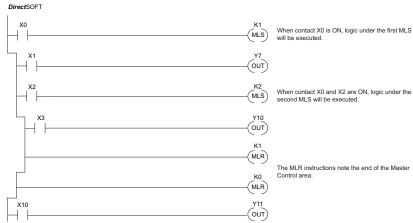

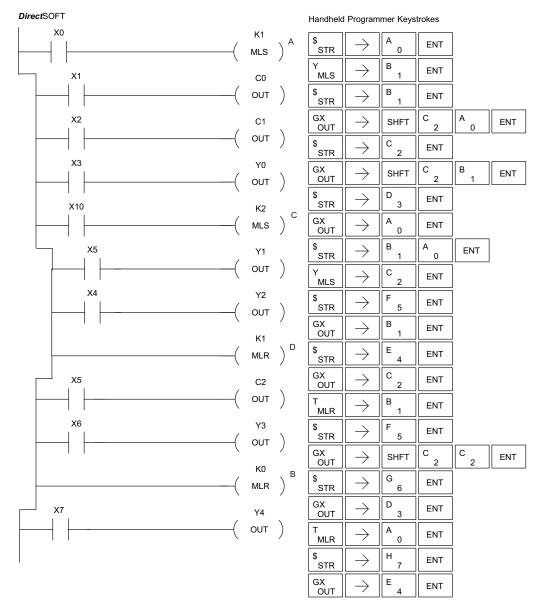

| Master Line Set (MLS)                        | 5-81 |

| Master Line Reset (MLR)                      | 5-81 |

| Understanding Master Control Relays          | 5-81 |

| MLS/MLR Example                              | 5-82 |

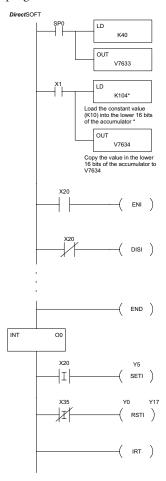

| Interrupt Instructions                       | 5-83 |

| Interrupt (INT)                              | 5-83 |

| Interrupt Return (IRT)                       | 5-83 |

| Interrupt Return Conditional (IRTC)          | 5-83 |

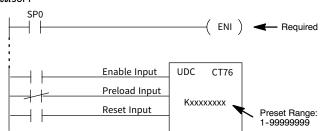

| Enable Interrupts (ENI)                      | 5-83 |

| Disable Interrupts (DISI)                    | 5-83 |

| External Interrupt Program Interrupt              | 5-84 |

|---------------------------------------------------|------|

| Message Instructions                              | 5-85 |

| Fault (FAULT)                                     | 5-85 |

| Fault Example                                     | 5-86 |

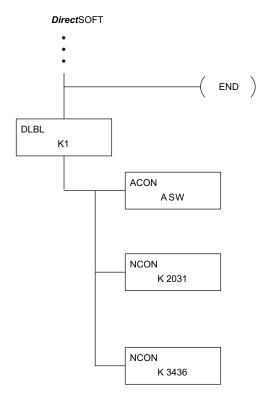

| Data Label (DLBL)                                 | 5-87 |

| ASCII Constant (ACON)                             | 5-87 |

| Numerical Constant (NCON)                         | 5-87 |

| Data Label Example                                | 5-88 |

|                                                   |      |

| <b>Chapter 6 - Drum Instruction Programming</b>   |      |

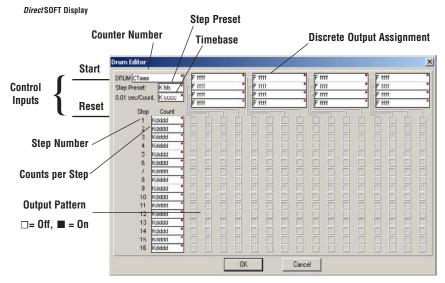

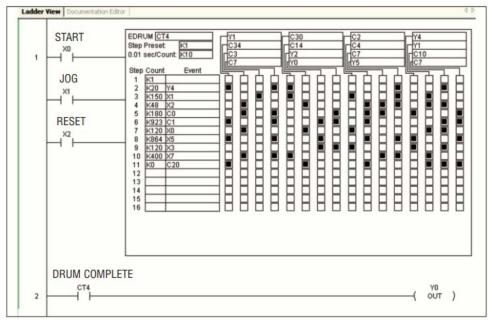

| Introduction                                      | 6-2  |

| Purpose                                           | 6-2  |

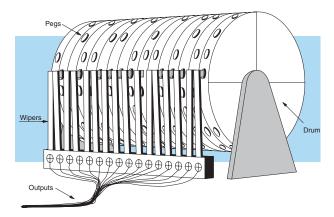

| Drum Terminology                                  | 6-2  |

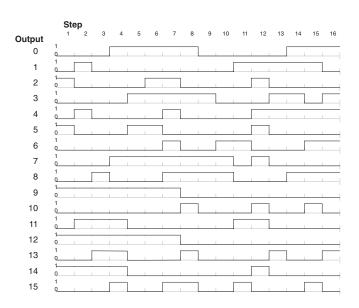

| Drum Chart Representation                         | 6-3  |

| Output Sequences                                  | 6-3  |

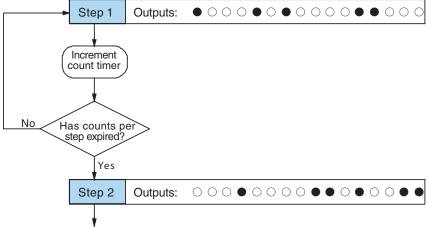

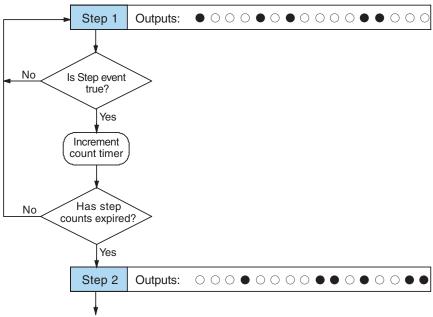

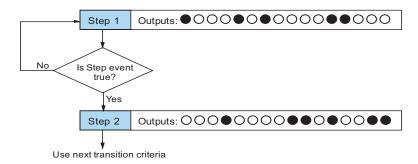

| Step Transitions                                  | 6-4  |

| Drum Instruction Parameters                       | 6-4  |

| Timer and Event Transitions                       | 6-5  |

| Event-Only Transitions                            | 6-6  |

| Counter Assignments                               | 6-6  |

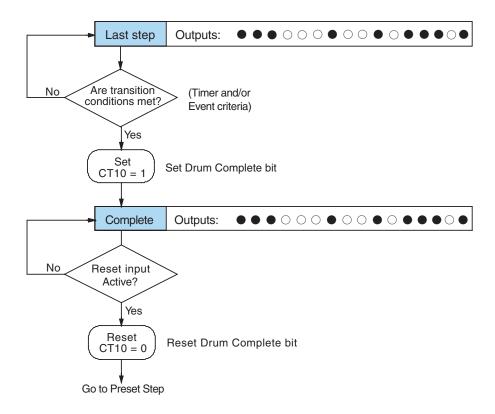

| Last Step Completion                              | 6-7  |

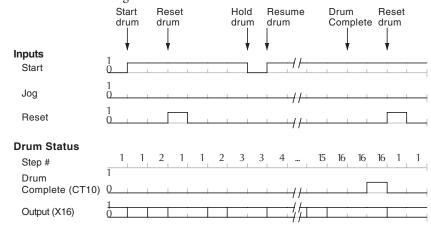

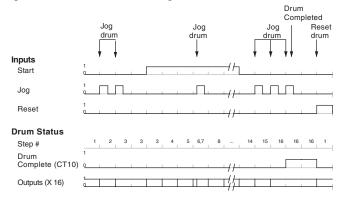

| Overview of Drum Operation                        | 6-8  |

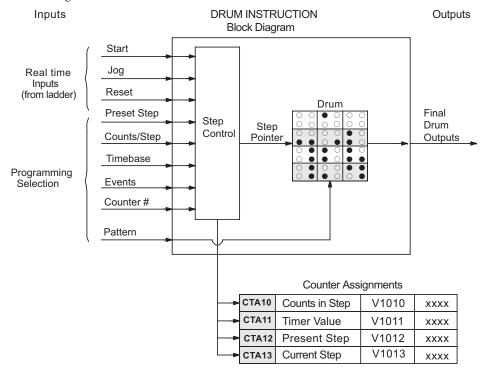

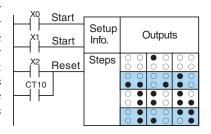

| Drum Instruction Block Diagram                    | 6-8  |

| Powerup State of Drum Registers                   | 6-9  |

| Drum Control Techniques                           | 6-10 |

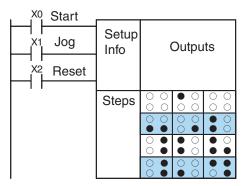

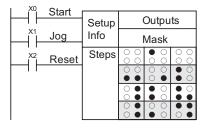

| Drum Control Inputs                               | 6-10 |

| Self-Resetting Drum                               | 6-11 |

| Initializing Drum Outputs                         | 6-11 |

| Using Complex Event Step Transitions              | 6-11 |

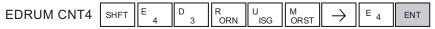

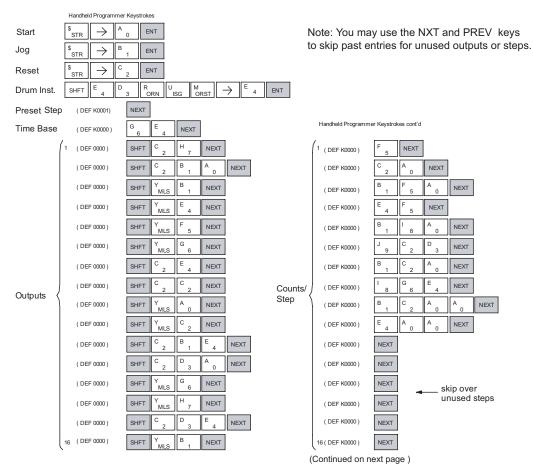

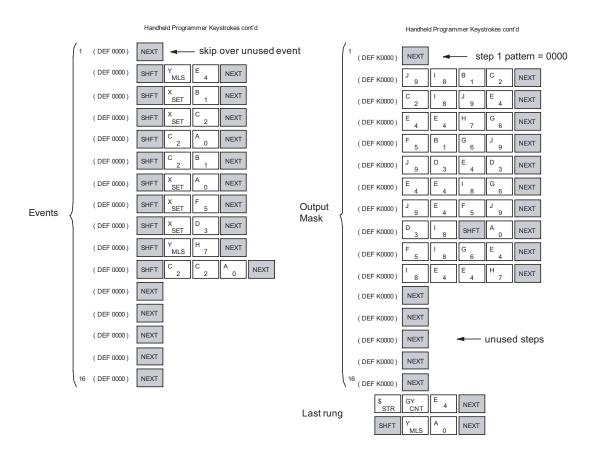

| Drum Instructions                                 | 6-12 |

| Handheld Programmer Drum Mnemonics                |      |

| -                                                 |      |

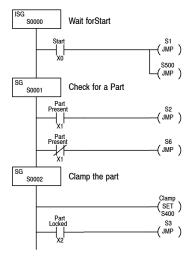

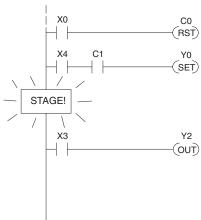

| Chapter 7 - RLL <sup>Plus</sup> Stage Programming |      |

| Introduction to Stage Programming                 | 7-2  |

| Overcoming "Stage Fright"                              | 7-2  |

|--------------------------------------------------------|------|

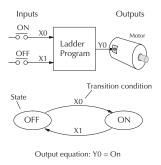

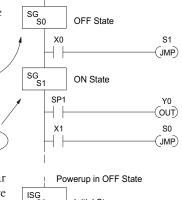

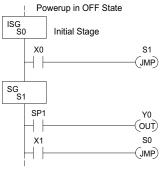

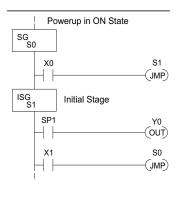

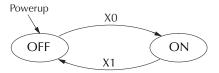

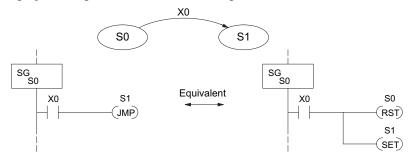

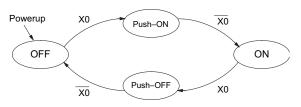

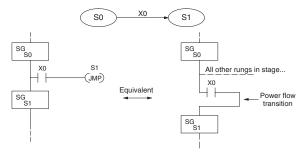

| Learning to Draw State Transition Diagrams             | 7-3  |

| Introduction to Process States                         |      |

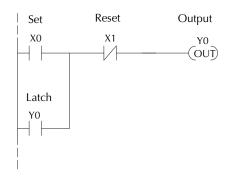

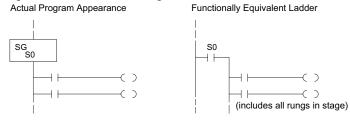

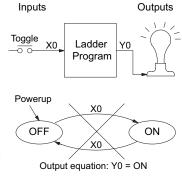

| RLL Equivalent                                         |      |

| Stage Equivalent                                       |      |

| Let's Compare                                          |      |

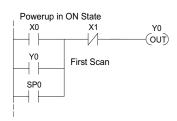

| Initial Stages                                         |      |

| What Stage Bits Do                                     |      |

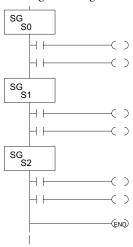

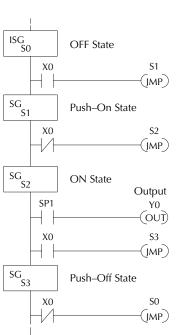

| Stage Instruction Characteristics                      | 7-6  |

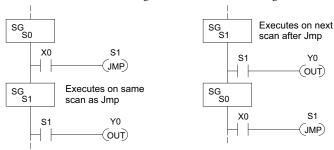

| Using the Stage Jump Instruction for State Transitions |      |

| Stage Jump, Set, and Reset Instructions                | 7-7  |

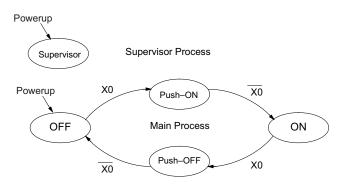

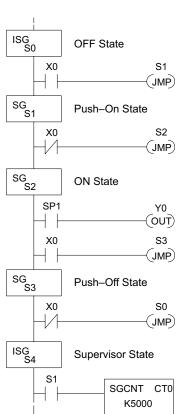

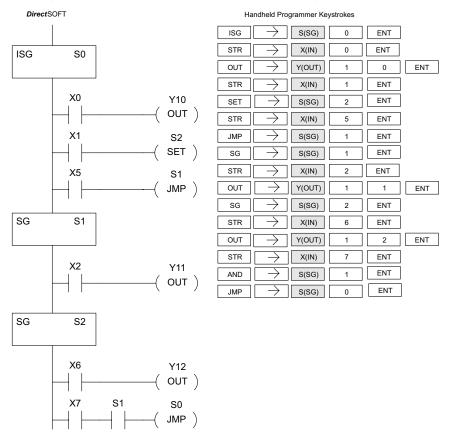

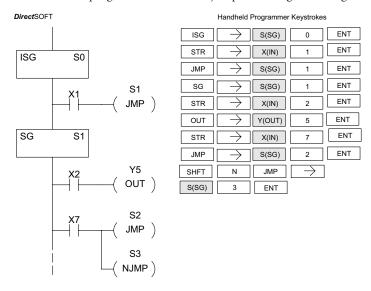

| Stage Program Example: Toggle On/Off Lamp Controller   | 7-8  |

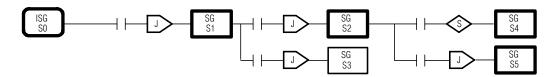

| Four Steps to Writing a Stage Program                  | 7-9  |

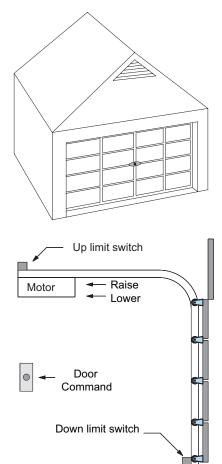

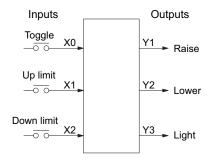

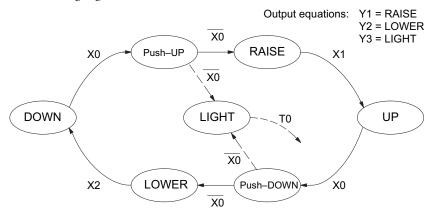

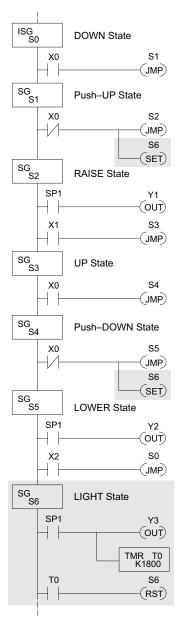

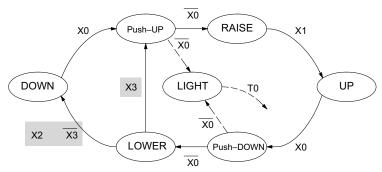

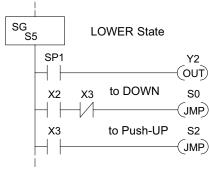

| Stage Program Example: A Garage Door Opener            | 7-10 |

| Garage Door Opener Example                             |      |

| Add Safety Light Feature                               | 7-12 |

| Stage Program Design Considerations                    |      |

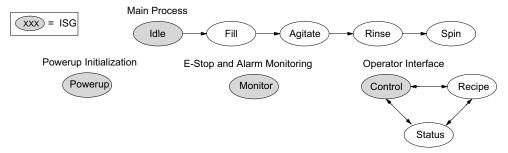

| Stage Program Organization                             | 7-15 |

| How Instructions Work Inside Stages                    | 7-16 |

| Using a Stage as a Supervisory Process                 | 7-17 |

| Stage Counter                                          | 7-17 |

| Power Flow Transition Technique                        |      |

| Stage View in <b>Direct</b> SOFT                       | 7-18 |

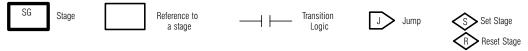

| RLLPLUS (Stage) Instructions                           | 7-19 |

| Stage (SG)                                             | 7-19 |

| Initial Stage (ISG)                                    | 7-20 |

| Jump (JMP)                                             | 7-20 |

| Questions and Answers about Stage Programming          | 7-22 |

|                                                        |      |

| Chapter 8 - Maintenance and Troubleshooting            |      |

| Hardware System Maintenance                            | 8-2  |

| Diagnostics                                            | 8-3  |

| V-memory Error Code Locations                               | 8-4  |

|-------------------------------------------------------------|------|

| Special Relays (SP) Corresponding to Error Codes            | 8-4  |

| DL105 Micro PLC Error Codes                                 | 8-5  |

| Program Error Codes                                         | 8-6  |

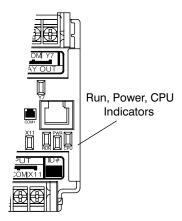

| CPU Error Indicators                                        | 8-7  |

| PWR Indicator                                               | 8-7  |

| Incorrect Base Power                                        | 8-7  |

| Faulty CPU                                                  | 8-7  |

| Run Indicator                                               | 8-8  |

| CPU Indicator                                               | 8-8  |

| Communications Problems                                     | 8-8  |

| I/O Point                                                   | 8-9  |

| Possible Causes                                             | 8-9  |

| Some Quick Steps                                            | 8-9  |

| Testing Output Points                                       | 8-10 |

| Handheld Programmer Keystrokes Used to Test an Output Point | 8-10 |

| Noise Troubleshooting                                       | 8-11 |

| Electrical Noise Problems                                   | 8-11 |

| Reducing Electrical Noise                                   | 8-11 |

| Machine Startup and Program Troubleshooting                 | 8-12 |

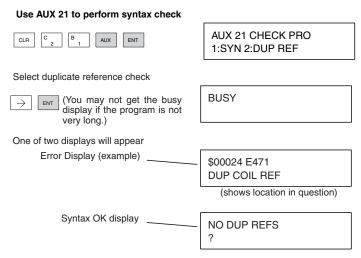

| Program Syntax Check                                        | 8-12 |

| Special Instructions                                        | 8-13 |

| Duplicate Reference Check                                   | 8-14 |

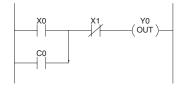

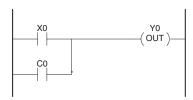

| Run Time Edits                                              | 8-15 |

| Forcing I/O Points                                          | 8-17 |

| Reset the PLC to Factory Defaults                           | 8-18 |

| Appendix A - Auxiliary Functions                            |      |

|                                                             |      |

| Introduction.                                               |      |

| Purpose of Auxiliary Functions                              |      |

| Accessing AUX Functions via DirectSOFT                      |      |

| Accessing AUX Functions via the Handheld Programmer         |      |

| AUX 2* — RLL Operations                                     |      |

| AUX 21 · Check Program                                      | A-4  |

### **Table of Contents**

| AUSX 22 · Change Reference                 | 4 |

|--------------------------------------------|---|

| AUX 23 · Clear Ladder Range                |   |

| AUX 24 · Clear Ladders                     | 4 |

| AUX 3* — V-memory Operations               | 4 |

| AUX 31 · Clear V- Memory                   | 4 |

| AUX 4* — I/O Configuration                 | 5 |

| AUX 41 Show I/O Configuration              | 5 |

| AUX 5* — CPU Configuration                 | 5 |

| AUX 51 · Modify Program Name               | 5 |

| AUX 53 · Display Scan Time                 | 5 |

| AUX 54 · Initialize Scratchpad             | 5 |

| AUX 55 · Set Watchdog Timer                | 5 |

| AUX 57 · Set Retentive Ranges              | 6 |

| AUX 58 · Test Operations                   | 6 |

| AUX 5B Counter Interface Configuration     | 6 |

| AUX 6* — Handheld Programmer Configuration | 6 |

| AUX 61 · Show Revision Numbers             | 6 |

| AUX 62 · Beeper On / Off                   | 7 |

| AUX 65 · Run Self Diagnostics              | 7 |

| AUX 7* — EEPROM Operations                 | 7 |

| Transferable Memory Areas                  | 7 |

| AUX 71 · CPU to HPP EEPROM                 | 7 |

| AUX 72 · HPP EEPROM to CPU                 | 7 |

| AUX 73 · Compare HPP EEPROM to CPU         |   |

| AUX 74 · HPP EEPROM Blank Check            |   |

| AUX 75 · Erase HPP EEPROM                  | 8 |

| AUX 76 · Show EEPROM Type                  | 8 |

| AUX 8* — Password Operations               | 8 |

| AUX 81 · Modify Password                   | 8 |

| AUX 82 · Unlock CPU                        | 9 |

| AUX 83 · Lock CPU                          | 9 |

|                                            |   |

| Appendix B - DL105 Error Codes             |   |

| DL105 Error Code Tables                    | 2 |

|                                            |   |

| Appendix C - Instruction Execution Times           |      |

|----------------------------------------------------|------|

| Introduction                                       | C-2  |

| V-Memory Data Registers                            |      |

| V-Memory Bit Registers                             |      |

| How to Read the Tables                             | C-2  |

| Instruction Execution Times                        | C-3  |

| Boolean Instructions                               | C-3  |

| Comparative Boolean Instructions, Continued        | C-4  |

| Comparative Boolean Instructions, Continued        | C-5  |

| Comparative Boolean Instructions, Continued        | C-6  |

| Immediate Instructions                             | C-6  |

| Timer, Counter, Shift Register, EDRUM Instructions | C-7  |

| Accumulator Data Instructions                      | C-8  |

| Logical Instructions                               | C-9  |

| Math Instructions                                  | C-9  |

| Bit Instructions                                   |      |

| Number Conversion Instructions                     | C-10 |

| Table Instructions                                 | C-10 |

| CPU Control Instructions                           | C-11 |

| Program Control Instructions                       | C-11 |

| Interrupt Instructions                             | C-11 |

| Message Instructions                               |      |

| RLL <sup>PLUS</sup> Instructions                   |      |

| Appendix D - Special Relays                        |      |

| DL105 PLC Special Relays                           | D-2  |

| Startup and Real-Time Relays                       | D-2  |

| CPU Status Relays                                  | D-2  |

| System Monitoring                                  | D-3  |

| Accumulator Status                                 | D-3  |

| Equal Relays for HSIO Mode 10 Counter Presets      | D-4  |

| Appendix E - DL105 PLC Memory                      |      |

| DI 105 PI C Memory                                 | F-2  |

| Appendix F - European Union Directives (CE)            |      |

|--------------------------------------------------------|------|

| European Union (EU) Directives                         | F-2  |

| General Safety                                         | F-4  |

| Other Sources of Information                           | F-4  |

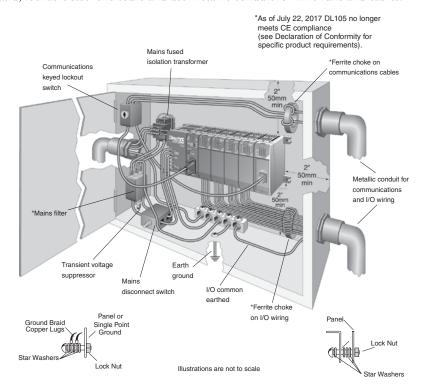

| Basic EMC Installation Guidelines                      | F-5  |

| Enclosures                                             | F-5  |

| Electrostatic Discharge (ESD)                          | F-5  |

| Suppression and Fusing                                 | F-6  |

| Internal Enclosure Grounding                           | F-6  |

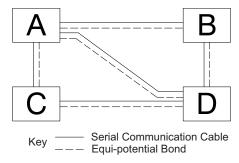

| Equipotential Grounding                                | F-7  |

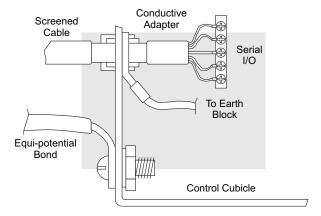

| Communications and Shielded Cables                     | F-7  |

| Analog and RS232 Cables                                | F-8  |

| Shielded Cables within Enclosures                      |      |

| Analog Modules and RF Interference                     |      |

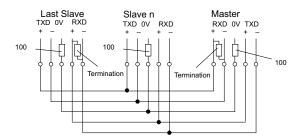

| Network Isolation                                      |      |

| DC Powered Versions                                    | F-9  |

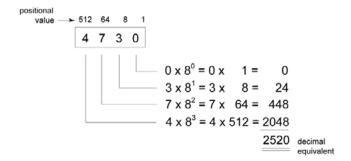

| Appendix G - Numbering Systems Introduction            | G-2  |

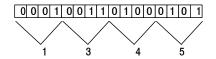

| Binary Numbering System                                |      |

|                                                        |      |

| Hexadecimal Numbering System                           |      |

| Octal Numbering System                                 | G-4  |

| Binary Coded Decimal (BCD) Numbering System            | G-5  |

| Real (Floating Point) Numbering System                 | G-6  |

| BCD/Binary/Decimal/Hex/Octal - What is the Difference? | G-7  |

| Data Type Mismatch                                     | G-8  |

| Signed vs. Unsigned Integers                           | G-9  |

| AutomationDirect.com Products and Data Types           | G-10 |

| DirectLOGIC PLCs                                       |      |

| C-more and C-more Micro Graphic Panels                 |      |

# CHAPTER 1

# **GETTING STARTED**

### In This Chapter...

| Introduction                                 | 1–2  |

|----------------------------------------------|------|

| Conventions Used                             | 1–3  |

| Programming Methods                          | 1–5  |

| I/O Quick Chart Selection                    | 1–6  |

| Quick Start for PLC Checkout and Programming | 1–7  |

| Steps to Designing a Successful System       | 1–11 |

| Ouestions and Answers about DL105 Micro PLCs | 1–13 |

**NOTE:** Modules F1-130-DD, F1-130-DD-D, F1-130AA, F1-130DA, F1-130DR-D, F1-130DR, F1-10CON, and F1-130AR have been discontinued. Terminal blocks B-F1130DR and B-F1130AR are also discontinued. Please consider Productivity, CLICK, or BRX systems as a replacement platform.

### Introduction

### The Purpose of this Manual

Thank you for purchasing a DL105 Micro PLC. This manual shows you how to install, program, and maintain all the Micro PLCs in the DL105 family. It also helps you understand how to interface them to other devices in a control system.

This manual contains important information for personnel who will install DL105 PLCs, and for the PLC programmer. If you understand PLC systems, our manuals will provide all the information you need to get and keep your system up and running.

### Where to Begin

If you already understand the DL105 Micro PLC please read Chapter 2, "Installation, Wiring, and Specifications", and proceed on to other chapters as needed. Be sure to keep this manual handy for reference when you run into questions. If you are a new DL105 customer, we suggest you read this manual completely so you can understand the wide variety of features in the DL105 family of products. We believe you will be pleasantly surprised with how much you can accomplish with **AutomationDirect** products.

### Supplemental Manuals

If you have purchased operator interfaces or *Direct*SOFT programming software, you will need to supplement this manual with the manuals that are written for these products.

### **Technical Support**

We realize that even though we strive to be the best, we may have arranged our information in such a way you cannot find what you are looking for. First, check these resources for help in locating the information:

- Table of Contents chapter and section listing of contents, in the front of this manual

- Appendices reference material for key topics, near the end of this manual

You can also check our online resources for the latest product support information:

Our Web site is:

### http://www.automationdirect.com

If you still need assistance, please call us at 770-844-4200. Our technical support group is glad to work with you in answering your questions. They are available Monday through Friday from 9:00 A.M. to 6:00 P.M. Eastern Standard Time.

### **Conventions Used**

**NOTE:** When you see the "notepad" icon in the left-hand margin, the paragraph to its immediate right will be a special note. The word **NOTE:** in boldface will mark the beginning of the text.

WARNING: When you see the "exclamation mark" icon in the left-hand margin, the paragraph to its immediate right will be a warning. This information could prevent injury, loss of property, or even death (in extreme cases). The entire WARNING: will be in boldface text.

### **Key Topics for Each Chapter**

The beginning of each chapter will list the key topics that can be found in that chapter.

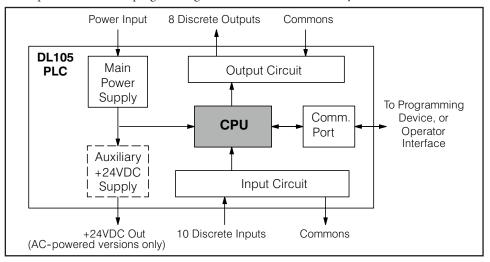

### **DL105 Micro PLC Components**

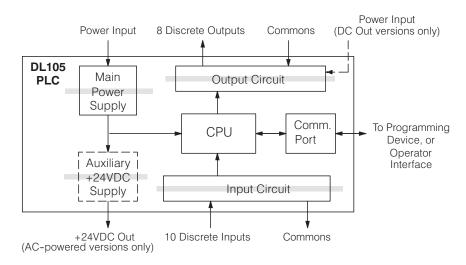

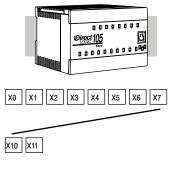

The DL105 Micro PLC family is a versatile product line that provides a wide variety of features in a very compact footprint. The PLCs are small, yet offer many features usually found in larger, more expensive systems. These include removable connectors, RS-232C communication port, and +24V auxiliary power supply.

### The DL105 Micro PLC Family

The DL105 Micro PLC family includes eight different versions. All have the same appearance and CPU performance. The CPU offers the same instruction set as our popular DL230 CPU, plus several more instructions specifically designed for machine control applications. All DL105 PLCs have an RS-232C communications port, and the AC-powered versions have an auxiliary +24V output. Units with DC inputs have selectable high-speed input features on four input points. Units with DC outputs offer selectable pulse output capability on the first two output points. All DL105 Micro PLCs offer a large amount of program memory, a substantial instruction set and advanced diagnostics. Details of these features and more are covered in Chapter 4, CPU Specifications and Operation. The eight types of DL105 Micro PLCs provide a variety of Input/Output choices, listed in the following table.

| DL105<br>Part Number    | Discrete<br>Input Type | Discrete<br>Output Type | External<br>Power | Auxiliary<br>24V Output | High-Speed<br>Input | Pulse<br>Output |

|-------------------------|------------------------|-------------------------|-------------------|-------------------------|---------------------|-----------------|

| F1-130AR<br>(retired)   | AC                     | Relay                   |                   |                         | No                  | No              |

| F1-130DR<br>(retired)   | DC                     | Relay                   |                   |                         | Yes                 | No              |

| F1-130AD                | AC                     | DC                      |                   |                         | No                  | Yes             |

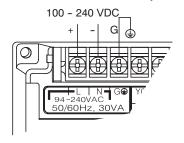

| F1-130DD<br>(retired)   | DC                     | DC                      | 94–240 VAC        | Yes                     | Yes                 | Yes             |

| F1-130AA<br>(retired)   | AC                     | AC                      |                   |                         | No                  | No              |

| F1-130DA<br>(retired)   | DC                     | AC                      |                   |                         | Yes                 | No              |

| F1-130DR-D              | DC                     | Relay                   |                   |                         | Yes                 | No              |

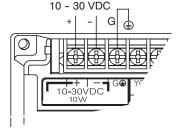

| F1-130DD-D<br>(retired) | DC                     | DC                      | 10-30 VDC         | No                      | Yes                 | Yes             |

**NOTE:** F1-130-DD, F1-130-DD-D, F1-130AA, F1-130AR, F1-130DR, and F1-130DA modules have been discontinued. Please consider Productivity, CLICK, or BRX systems as a replacement platform.

### **Programming Methods**

Two programming methods are available: a software programming package and a handheld programmer. The software and the handheld programmer support RLL (Relay Ladder Logic) and RLLPLUS (STAGE) programming.

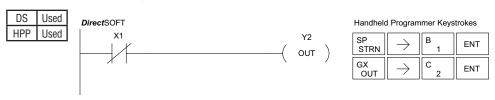

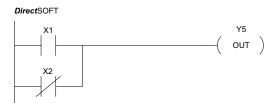

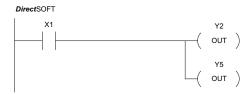

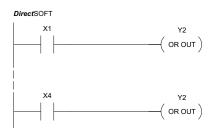

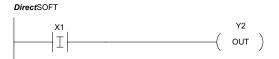

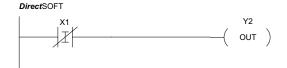

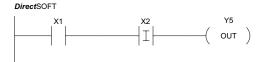

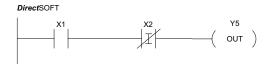

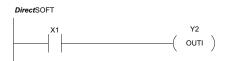

### DirectSOFT Programming for Windows

The DL105 Micro PLC can be programmed with one of the most advanced programming packages in the industry - - *Direct*SOFT, a Windows-based software package that supports familiar features such as cut-and-paste between applications, point-and-click editing, viewing and editing multiple application programs at the same time, etc. *Direct*SOFT universally supports the *Direct*LOGIC CPU families. This means that you can use the same *Direct*SOFT package to program DL05, DL06, DL105, DL205, DL305, DL405 or any new CPU we may add to our product line. (Upgrade software may be required for new CPUs as they become available.)

There is a separate manual that discusses the *Direct*SOFT programming software which is included with your software package.

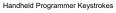

### Handheld Programmer

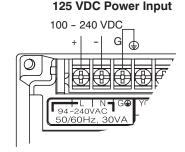

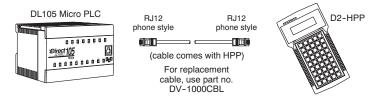

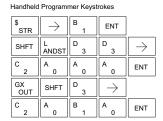

All DL105 Micro PLCs have a built-in programming port for use with the handheld programmer (D2-HPP), the same programmer used with the DL205 family. The handheld programmer can be used to create, modify and debug your application program. A separate manual discusses the Handheld Programmer.

### I/O Quick Chart Selection

The eight versions of the DL105 have Input/Output circuits which can interface to a wide variety of field devices. In several instances a particular Input or Output circuit can interface to either DC or AC voltages, or both sinking and sourcing circuit arrangements. Check this chart carefully to find the proper DL105 Micro PLC to interface to the field devices in your application.

| Dooloon                 | INPUTS               |                   |                                  | OUTPUTS             |                   |                                                           |

|-------------------------|----------------------|-------------------|----------------------------------|---------------------|-------------------|-----------------------------------------------------------|

| Boolean<br>Instructions | I/O Type/<br>Commons | Sink/<br>Source   | Voltage<br>Ranges                | I/O Type<br>Commons | Sink/<br>Source   | Voltage/Current<br>Ratings                                |

| F1-130AR                | AC / 3               |                   | 80 - 132 VAC<br>90 - 150 VDC     | Relay / 4           | Sink or<br>Source | 12–30 VDC, 7A <sup>*</sup><br>12–250 VAC, 7A <sup>*</sup> |

| F1-130DR                | DC / 3               | Sink or<br>Source | 10 - 26.4 VDC<br>21.6 - 26.4 VAC | Relay / 4           | Sink or<br>Source | 12–30 VDC, 7A <sup>*</sup><br>12–250 VAC, 7A <sup>*</sup> |

| F1-130AD                | AC / 3               |                   | 80 - 132 VAC<br>90 - 150 VDC     | DC / 1**            | Sink              | 5–30 VDC, 0.3 A (Y0–Y1)<br>5–30 VDC, 0.6 A (Y3–Y7)        |

| F1-130DD                | DC / 3               | Sink or<br>Source | 10 - 26.4 VDC<br>21.6 - 26.4 VAC | DC / 1**            | Sink              | 5–30 VDC, 0.3 A (Y0–Y1)<br>5–30 VDC, 0.6 A (Y3–Y7)        |

| F1-130AA                | AC / 3               |                   | 80 - 132 VAC<br>90 - 150 VDC     | AC / 4              |                   | 20–140 VAC, 47–63 Hz<br>1.7 A <sup>*</sup>                |

| F1-130DA                | DC / 3               | Sink or<br>Source | 10 - 26.4 VDC<br>21.6 - 26.4 VAC | AC / 4              |                   | 20–140 VAC, 47–63 Hz<br>1.7 A <sup>*</sup>                |

| F1-130DR-D              | DC / 3               | Sink or<br>Source | 10 - 26.4 VDC<br>21.6 - 26.4 VAC | Relay / 4           | Sink or<br>Source | 12–30 VDC, 7A <sup>*</sup><br>12–250 VAC, 7A <sup>*</sup> |

| F1-130DD-D              | DC / 3               | Sink or<br>Source | 10 - 26.4 VDC<br>21.6 - 26.4 VAC | DC / 1**            | Sink              | 5–30 VDC, 0.3 A (Y0–Y1)<br>5–30 VDC, 0.6 A (Y3–Y7)        |

<sup>\*</sup> Subject to temperature derating chart. See Chapter 2 Specifications for your particular DL105 version.

**NOTE:** Modules F1-130-DD, F1-130-DD-D, F1-130AA, F1-130DA, F1-130DR-D, F1-130DR, F1-10CON, and F1-130AR have been discontinued. Terminal blocks B-F1130DR and B-F1130AR are also discontinued. Please consider Productivity, CLICK, or BRX systems as a replacement platform.

<sup>\*\*</sup> DC outputs have one electrical common, but it is accessible at three terminals on the output connector.

### **Quick Start for PLC Checkout and Programming**

If you have experience with PLCs, or if you just want to setup a quick example, this example is for you! This example is not intended to tell you everything you need to start-up your system, warnings and helpful tips are in the rest of the manual. It is only intended to give you a general picture of what you will need to do to get your system powered-up.

### Step 1: Unpack the Recommended DL105 Equipment

Unpack the DL105 equipment and verify you have the recommended parts necessary to build this demonstration system. The components are:

- DL105 Micro PLC

- AC power cord for AC-powered units

- F1- 04SIM input simulator, or toggle switches (see Step 2 on next page).

- Hook-up wire, 16-20 AWG

- DL105 User Manual (this manual)

- A small screwdriver, regular or #2 Philips type

You will need at least one of the following programming options:

- DirectSOFT Programming Software, DirectSOFT Manual, and a programming cable (connects the DL105 to a personal computer),or

- D2- HPP Handheld Programmer (comes with programming cable), and the Handheld Programmer Manual

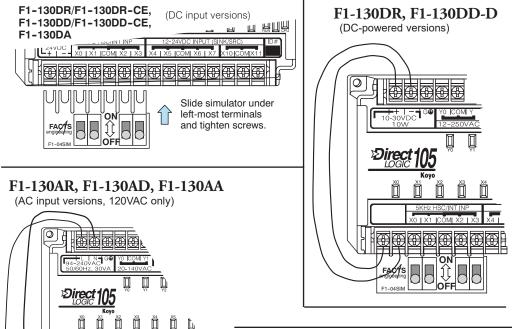

### Step 2: Connect Switches to Input Terminals

To finish this quick-start exercise or study other examples in this manual, you'll need to connect some input switches as shown below. For most models, the F1-04SIM Input Simulator is a quick way to install four switches on inputs X0 - X3. DC-powered units will require routing DC power to the simulator as shown. We recommend using one of the models compatible with the input simulator as you learn the DL105.

However, you may wire individual toggle switches to AC-powered units as shown, as long as you follow the instructions in the accompanying WARNING note.

Toggle Switches, UL Listed

WARNING: DO NOT wire the toggle switches as shown to 240VAC-powered units. The discrete inputs will only accept 120VAC nominal. Also, remove power and unplug the DL105 when wiring the switches. Only use UL-approved switches rated for at least 250VAC, 1A. Firmly mount the switches before using.

NEVER use the input simulator on these units with AC-type discrete inputs.

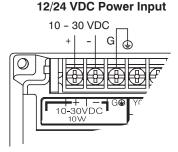

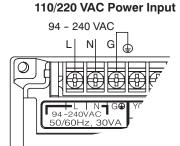

### Step 3: Connect the Power Wiring

Connect the power input wiring for the version DL105 you have. Observe all precautions stated earlier in this manual. For more details on wiring, see Chapter 2 on Installation, Wiring, and Specifications. When the wiring is complete, close the connector covers. Do not apply power at this time.

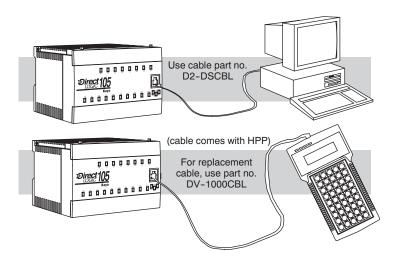

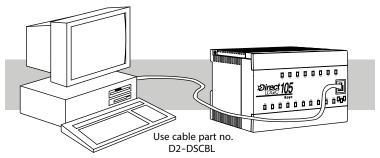

### Step 4: Connect the Programming Device

Most programmers will use *Direct*SOFT programming software, installed on a personal computer. Or, you may need the portability of the Handheld Programmer. Both devices will connect the COM1 port of the DL105 via the appropriate cable.

### Step 5: Switch on the System Power

Apply power to the system and ensure the PWR indicator on the DL105 is on. If not, remove power from the system and check all wiring and refer to the troubleshooting section in Chapter 8 for assistance.

### **Step 6: Initialize Scratchpad Memory**

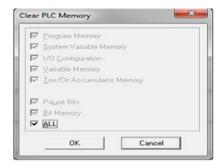

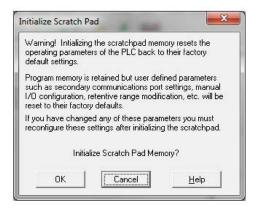

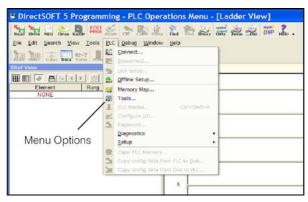

It's a good precaution to always clear the system memory (scratchpad memory) on a new DL105. When a unit has been without power for several days, the system RAM contents may have been corrupted and will require initialization.

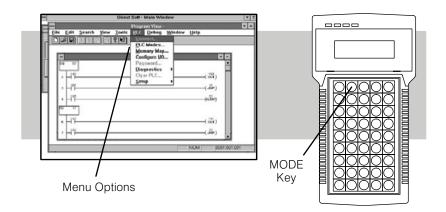

- In *Direct*SOFT, select the PLC Menu > Setup > Initialize Scratchpad. For additional information, see the *Direct*SOFT Manual.

- For the Handheld Programmer, use the AUX key and execute AUX 54.

For additional information, see the Handheld Programmer Manual.

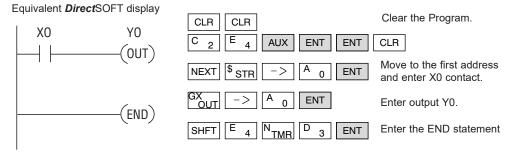

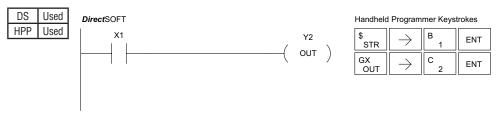

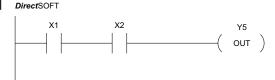

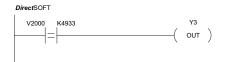

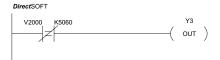

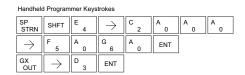

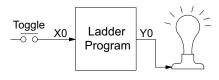

### Step 7: Enter a Ladder Program

At this point, *Direct*SOFT programmers need to refer to the Quick Start Tutorial in the *Direct*SOFT Manual. There you will learn how to establish a communications link with the DL105 PLC, change CPU modes to Run or Program, and enter a program.

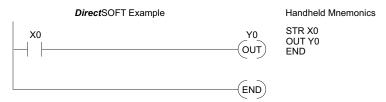

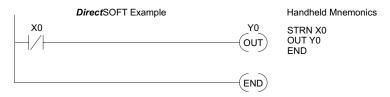

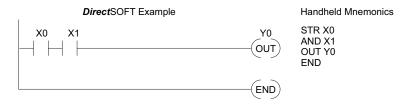

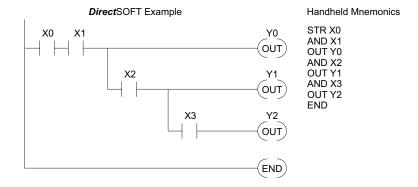

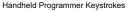

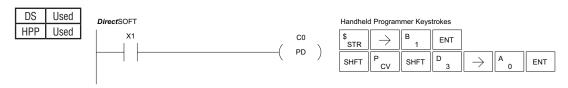

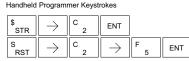

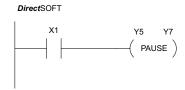

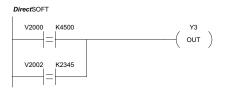

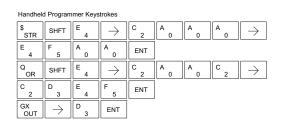

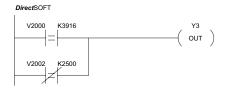

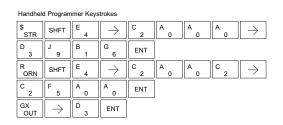

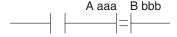

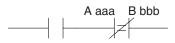

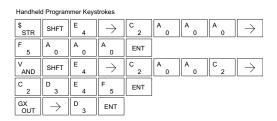

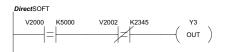

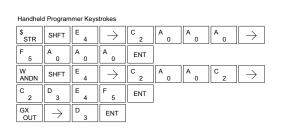

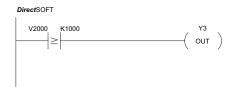

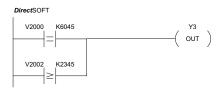

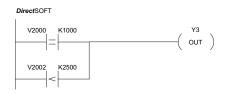

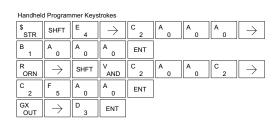

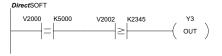

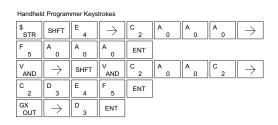

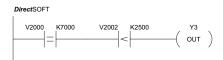

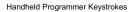

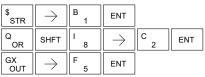

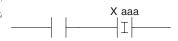

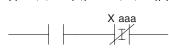

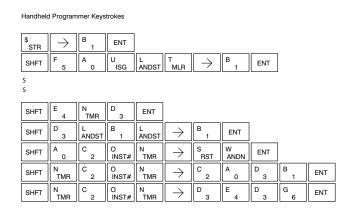

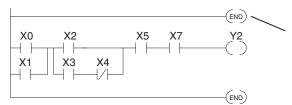

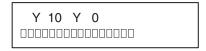

If you are learning how to program with the Handheld Programmer, make sure the CPU is in Program Mode (the RUN LED on the front of the DL105 should be off.) If the RUN LED is on, use the MODE key on the Handheld Programmer to put the PLC in Program Mode. Enter the following keystrokes on the Handheld Programmer.

After entering the simple example program put the PLC in Run mode by using the Mode key on the Handheld Programmer.

The RUN indicator on the PLC will illuminate indicating the CPU has entered the Run mode. If not, repeat this step, ensuring the program is entered properly or refer to the troubleshooting guide in chapter 8.

After the CPU enters the run mode, the output status indicator for Y should follow the switch status on input channel X0. When the switch is on, the output will be on.

### **Steps to Designing a Successful System**

### Step 1: Review the Installation Guidelines

Always make safety the first priority in any system design. Chapter 2 provides several guidelines that will help you design a safer, more reliable system. This chapter also includes wiring guidelines for the various versions of the DL105 PLC.

### Step 2: Understand PLC Setup Procedures

The PLC is the heart of your automation system. Make sure you take time to understand the various features and setup requirements.

### Step 3: Review the I/O Selection Criteria

There are many considerations involved when you select your I/O type and field devices. Take time to understand how the various types of sensors and loads can affect your choice of I/O type.

### Step 4: Choose a System Wiring Strategy

It is important to understand the various system design options that are available before wiring field devices and field-side power supplies to the Micro PLC.

### Step 5: Understand the System Operation

Before you begin to enter a program, it is very helpful to understand how the DL105 system processes information. This involves not only program execution steps, but also involves the various modes of operation and memory layout characteristics.

### Step 6: Review the Programming Concepts

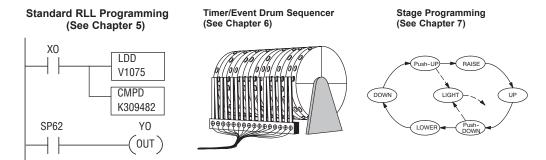

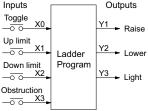

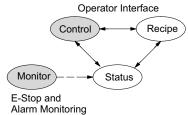

The DL105 PLC instruction set provides for three main approaches to solving the application program, depicted in the figure below.

- RLL diagram-style programming is the best tool for solving boolean logic and general CPU register/accumulator manipulation. It includes dozens of instructions, which will also be needed to augment drums and stages.

- The Timer/Event Drum Sequencer features up to 16 steps and offers both time and/or event-based step transitions. The EDRUM instruction is best for a repetitive process based on a single series of steps.

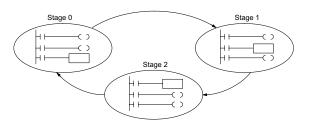

- Stage programming (also called RLLPLUS) is based on state-transition diagrams. Stages divide the ladder program into sections which correspond to the states in a flow chart you draw for your process.

After reviewing the programming concepts above, you'll be equipped with a variety of tools to write your application program.

### Step 7: Choose the Instructions

Once you have installed the Micro PLC and understand the main programming concepts, you can begin writing your application program. At that time you will begin to use one of the most powerful instruction sets available in a small PLC.

TMR

K30

# Step 8: Understand the Maintenance and Troubleshooting Procedures

Sometimes equipment failures occur when we least expect it. Switches fail, loads short and need to be replaced, etc. In most cases, the majority of the troubleshooting and maintenance time is spent trying to locate the problem. The DL105 Micro PLC has many built-in features such as error codes that can help you quickly identify problems.

CNT

CT3

### **Questions and Answers about DL105 Micro PLCs**

### Q. What is the instruction set like?

**A.** The instruction set is very close to our popular DL230 CPU. However, there are significant additions, such as the drum instruction and High-Speed I/O capability.

# Q. Do I have to buy the full *Direct*SOFT programming package to program the DL105?

A. No, *Direct*SOFT100R can be used. It has the same features as the full version of *Direct*SOFT5 but allows only 100 words of ladder code that can be downloaded to the PLC. It will also program DL05/06/205/305/405 systems, and it is only available for download online. (Order programming cable separately.) 32- bit application, Windows 2000 or Windows XP (Pro or Home) recommended. This software is available at no cost to you.

### Q. Is the DL105 networkable or expandable?

**A.** No, the DL130 series is stand-alone PLCs. However, our DL205 system is expandable and networkable (with DL240 CPU), yet very compact and affordable.

### Q. Does the DL105 have motion control capability?

**A.** Yes. The High-Speed I/O features offer either encoder inputs with high-speed counting and presets with interrupt, or a pulse/direction output for stepper control. Three types of motion profiles are available, which are explained in Chapter 3.

### Q. Are the ladder programs stored in a removable EPROM?

**A.** The DL105 contains a non-removable EEPROM for program storage, which may be written and erased thousands of times. You may transfer programs to/from *Direct*SOFT on a PC, or the HPP (which does support a removable EEPROM).

### Q. Does the DL105 contain fuses for its outputs?

**A.** There are no output circuit fuses. Therefore, we recommend fusing each channel, or fusing each common. See Chapter 2 for I/O wiring guidelines.

### Q. Is the DL105 Micro PLC U.L.R approved?

**A.** The Micro PLC has met the requirements of UL (Underwriters' Laboratories, Inc.) and CUL (Canadian Underwriters' Laboratories, Inc.).

### Q. Can the DL105 accept 5VDC inputs?

**A.** No, 5 volts is lower than the DC input ON threshold. However, many TTL logic circuits can drive the inputs if they are wired as open collector (sinking) inputs. See Chapter 2 for I/O wiring guidelines.

### Q. Which devices can I connect to the Com1 port of the DL105?

- **A.** The port is RS-232C, fixed at 9600 baud, and uses the proprietary K-sequence protocol. The port communicates with the following devices:

- DV-1000 Data Access Unit or Optimation Operator interface panels

- *Direct*SOFT (running on a personal computer)

- D2-HPP handheld programmer

- Other devices which communicate via K-sequence protocol should work with the DL105 Micro PLC. Contact the vendor for details.

# Installation, Wiring and Specifications

### In This Chapter...

| Safety Guidelines                  | 2–2  |

|------------------------------------|------|

| Orientation to DL105 Front Panel   | 2–5  |

| Mounting Guidelines                | 2–7  |

| Wiring Guidelines                  | 2–11 |

| System Wiring Strategies           | 2–14 |

| Wiring Diagrams and Specifications | 2–30 |

| Glossary of Specification Terms    | 2–54 |

**NOTE:** Modules F1-130-DD, F1-130-DD-D, F1-130AA, F1-130DA, F1-130DR-D, F1-130DR, F1-10CON, and F1-130AR have been discontinued. Terminal blocks B-F1130DR and B-F1130AR are also discontinued. Please consider Productivity, CLICK, or BRX systems as a replacement platform.

# **Safety Guidelines**

WARNING: Providing a safe operating environment for personnel and equipment is your responsibility and should be your primary goal during system planning and installation. Automation systems can fail and may result in situations that can cause serious injury to personnel or damage to equipment. Do not rely on the automation system alone to provide a safe operating environment. You should use external electromechanical devices, such as relays or limit switches, that are independent of the PLC application to provide protection for any part of the system that may cause personal injury or damage.

Every automation application is different, so there may be special requirements for your particular application. Make sure you follow all national, state, and local government requirements for the proper installation and use of your equipment.

# Plan for Safety

The best way to provide a safe operating environment is to make personnel and equipment safety part of the planning process. You should examine every aspect of the system to determine which areas are critical to operator or machine safety. If you are not familiar with PLC system installation practices, or your company does not have established installation guidelines, you should obtain additional information from the following sources.

- NEMA The National Electrical Manufacturers Association, located in Washington, D.C., publishes many different documents that discuss standards for industrial control systems. You can order these publications directly from NEMA. Some of these include: ICS 1, General Standards for Industrial Control and Systems;

- ICS 3, Industrial Systems;

- ICS 6, Enclosures for Industrial Control Systems

- NEC The National Electrical Code provides regulations concerning the installation and use of various types of electrical equipment. Copies of the NEC Handbook can often be obtained from your local electrical equipment distributor or your local library.

- Local and State Agencies many local governments and state governments have additional requirements above and beyond those described in the NEC Handbook. Check with your local Electrical Inspector or Fire Marshall office for information.

# **Safety Techniques**

The publications mentioned provide many ideas and requirements for system safety. At a minimum, you should follow these regulations. Also, you should use the following techniques, which may help reduce the risk of safety concerns.

- Orderly system shutdown sequence in the PLC control program.

- System power disconnects (guard limits, emergency stop switches, etc.)

### Three Levels of Protection

The aforementioned publications provide many ideas and requirements for system safety. At a minimum, you should follow these regulations. Also, you should use the following techniques, which provide three levels of system control.

- An orderly system shutdown sequence in the PLC control program

- A mechanical disconnect for output module power

- An emergency stop switch for disconnecting system power

# **Emergency Stops**

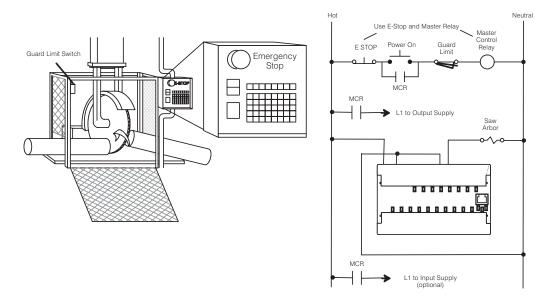

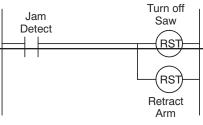

It is recommended that emergency stop circuits be incorporated into the system for every machine controlled by a PLC. For maximum safety in a PLC system, these circuits must not be wired into the controller, but should be hardwired external to the PLC. The emergency stop switches should be easily accessed by the operator and are generally wired into a master control relay (MCR) or a safety control relay (SCR) that will remove power from the PLC I/O system in an emergency.

MCRs and SCRs provide a convenient means for removing power from the I/O system during an emergency situation; by de–energizing an MCR (or SCR) coil, power to the input (optional) and output devices is removed. This event occurs when any emergency stop switch opens. However, the PLC continues to receive power and operate even though all its inputs and outputs are disabled.

The MCR circuit could be extended by placing a PLC fault relay (closed during normal PLC operation) in series with any other emergency stop conditions. This would cause the MCR circuit to drop the PLC I/O power in case of a PLC failure (memory error, I/O communications error, etc.).

# **Emergency Power Disconnect**

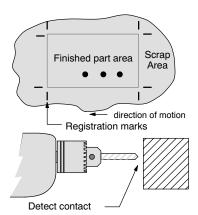

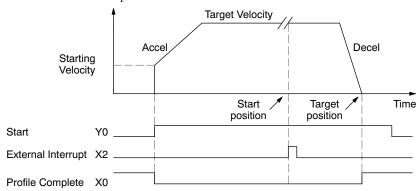

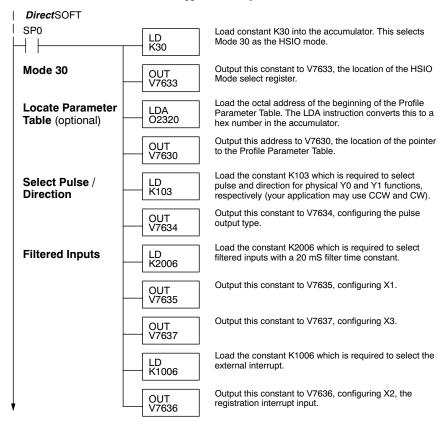

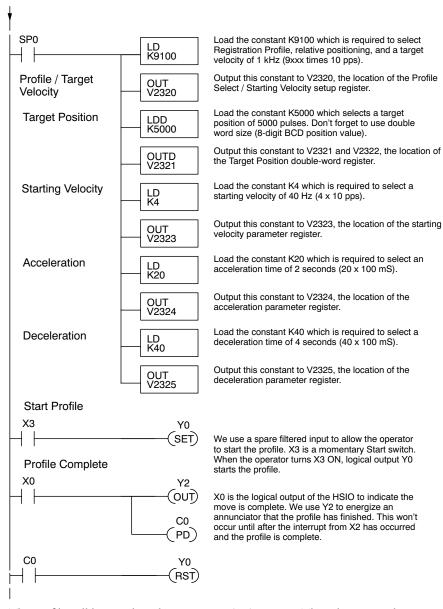

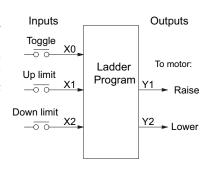

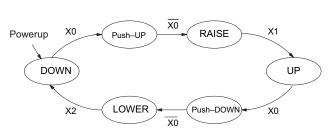

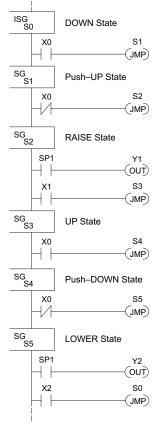

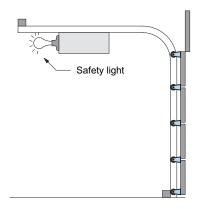

A properly rated emergency power disconnect should be used to power the PLC controlled system as a means of removing the power from the entire control system. It may be necessary to install a capacitor across the disconnect to protect against a condition known as "outrush". This condition occurs when the output triacs are turned off by powering off the disconnect, thus causing the energy stored in the inductive loads to seek the shortest distance to ground, which is often through the triacs.